# A 3.8-6.4GHz Local Oscillator System Using an Injection-Locked Frequency Doubling and Phase Tuning Technique

by

# James P. Maligeorgos

A thesis submitted in conformity with the requirements for the degree of Master of Applied Science Department of Electrical and Computer Engineering University of Toronto

Toronto, Ontario, Canada

© Copyright by James P. Maligeorgos 2001

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-58795-9

# A 3.8-6.4GHz Local Oscillator System Using an Injection-Locked Frequency Doubling and Phase Tuning Technique

James P. Maligeorgos

Graduate Department of Electrical and Computer Engineering

University of Toronto

Degree of Master of Applied Science, 2001

#### **Abstract**

This thesis studies the design of a novel local oscillator system based on low-voltage and low-power regenerative (injection locking) techniques. The LO system converts an input signal of frequency  $f_{LO}/2$  into a quadrature pair of LO signals at a frequency of  $f_{LO}$ , intended to drive a pair of I and Q down-converting mixers. A new IC compatible technique for regenerative frequency doubling is presented. Regenerative frequency doublers are cascaded on-chip to provide a net multiply-by-4 function, generating frequencies in excess of  $\frac{f_T}{2}$  without the need for interstage filtering. A new technique is also presented for frequency-independent phase control of the quadrature LO signals of a regenerative divider (I-Q generator), achieving a precision on the order of  $0.01^{\circ}$ . Results are presented in the context of a fabricated 5-6GHz image reject receiver.

# **Acknowledgments**

First and foremost, I would like to thank Professor John R. Long for going far beyond what is required of a supervising professor on a regular basis and for his part in the design of this chip. Without your contribution I would not have had the wonderful experience of presenting our work at ISSCC2000. You have been a great mentor. Thank you very much and I wish you the best of luck and much success in your future endeavours.

This work would not have been possible without the (much appreciated) financial support of the Natural Sciences and Engineering Research Council of Canada (NSERC). I am also indebted to the Canadian Microelectronics Corporation (CMC) for providing such an important and well executed service to Canadian universities. I would also like to thank Nortel for allowing CMC members access to their technology and for providing fabrication services for this work.

To all my colleagues who have passed through or still reside in EA104 and EA105, thank you for being such good friends and for being so much fun to work with. I wish you all eternal happiness and great success.

To my loving parents and my wonderful sister, Joyce, for all their love, support and endless encouragement, thank you, I couldn't have gone this far without you.

Finally, I would like to thank God for letting me live such a blessed life.

# **Table of Contents**

| Abstract                                                            |

|---------------------------------------------------------------------|

| Acknowledgments                                                     |

| Chapter 1: Introduction                                             |

| 1.1 Introduction                                                    |

| 1.2 Next Generation Wireless LAN                                    |

| 1.2.1 Frequency Specifications and System Design Challenges         |

| 1.3 Organization of this thesis                                     |

| Chapter 2: The Local Oscillator System                              |

| 2.1 The Basic Superheterodyne Receiver                              |

| 2.2 The Image band in a Heterodyne Receiver                         |

| 2.3 Filtering out the Image Band                                    |

| 2.4 Image-Reject Mixing                                             |

| 2.5 5-6 GHz Receiver Architecture                                   |

| 2.5.1 Overview of the Receiver Front-End                            |

| 2.6 LO System Overview                                              |

| 2.7 IC Fabrication Technology Overview                              |

| 2.8 LO System Operating/Design Requirements                         |

| 2.9 Quadrature Signal Generators2                                   |

| 2.10 IC Compatible Methods of Frequency Doubling                    |

| 2.10.1 Frequency Multiplier Using Unbalanced Emitter-Coupled Pairs3 |

| 2.10.2 Balun Transformer with Differential-Pair Doubler             |

| 2.10.3 An Emitter-Coupled Transistor Pair Frequency Doubler3        |

| 2.11 Summary of IC Frequency Doublers                               |

| Chapter 3: Injection Locked Ring Oscillators3                       |

| 3.1 Injection Locking of Oscillators                                |

| 3.2 Simulink Modeling4                                              |

| 3.3 Injection-Locked Ring Oscillators                               |

| 3.3.1 Simulink Model versus HSPICE Simulation                       |

| 3.4 ILRO Model Observations                                         |

| 3.4.1 Estimating the Injection Locking Range                        |

|         | 3.4.2 Some ILO Applications                                           |

|---------|-----------------------------------------------------------------------|

| Chapter | 4: Regenerative Frequency Doubling54                                  |

| 4.1     | Concept Introduction                                                  |

| 4.2     | A Fundamentally-Locked Regenerative Frequency Doubler56               |

|         | 4.2.1 Emitter-Coupled Doubling Mechanism59                            |

|         | 4.2.2 I-Q Phase Errors in the Ring due to Injection                   |

| 4.3     | Regenerativ € Doubler Variations                                      |

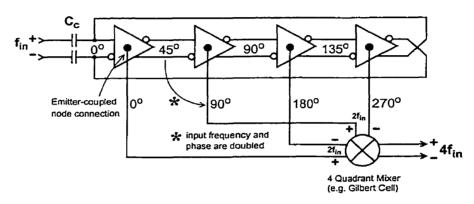

|         | 4.3.1 Regemerative Frequency Quadrupler                               |

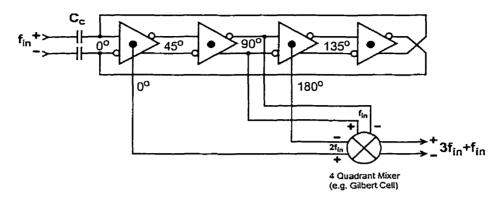

|         | 4.3.2 Regemerative Frequency Tripler                                  |

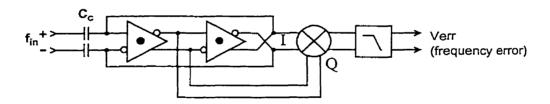

|         | 4.3.3 Frequency Tracking ILRO65                                       |

| 4.4     | Conclusion on Regenerative Frequency Doubling                         |

| Chapter | 5: A Frequency Halver with Precision Phase Tuning                     |

| 5.1     | A Regenerative Frequency Halver (Divider)                             |

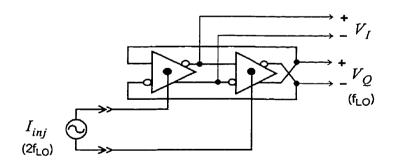

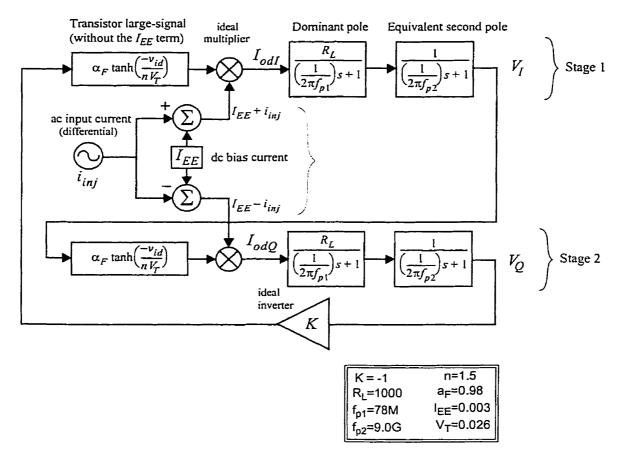

| 5.2     | Simulink Model of the Regenerative Frequency Divider                  |

| 5.3     | Precise Phase Control of Quadrature LO Signals                        |

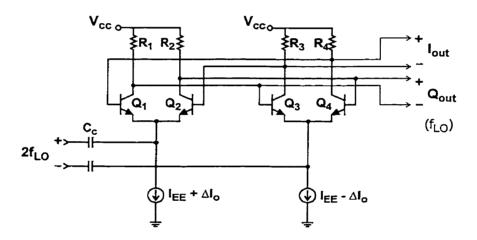

| 5.4     | Frequency Halver                                                      |

| Chapter | 6: A Regenerative LO System for a 5-6GHz Integrated Receiver 72       |

| 6.1     | Local Oscillator System Architecture and Design                       |

|         | 6.1.1 Selection of Free-Running Frequency                             |

|         | 6.1.2 Transistor Sizing                                               |

| 6.2     | First Frequency Doubling Stage                                        |

|         | 6.2.1 Setting the Free-Running Frequency and Determining Amplitude 77 |

|         | 6.2.2 Equivalent Injection-Load Network                               |

| 6.3     | Second Frequency Doubling Stage89                                     |

| 6.4     | Quadrature Signal Generator / Frequency Halver93                      |

| 6.5     | Divide-by-2 Prescaler / Low Frequency Halver95                        |

| 6.6     | LO System Design - Summary95                                          |

| Chapter | 7: Layout, Test and Measurement96                                     |

| 7.1     | Layout                                                                |

| 7.2     | Test Fixture and Setup98                                              |

#

# List of Tables

| Table 1.1  | Comparison of various WLAN standards [4,2,3]                                        | 1  |

|------------|-------------------------------------------------------------------------------------|----|

| Table 2.1  | LO system design, target specifications                                             | 2  |

| Table 3.1  | Comparison of the Locking Boundaries for Einj = 50mV-pk Injection                   | 52 |

| Table 6.1: | First doubling stage design parameters.                                             | 80 |

| Table 6.2: | Amplitude simulated and approximated values                                         | 8  |

| Table 6.3: | Circuit design parameters for the 4-stage doubler in Figure 6.4 (2.2 Volt supply)   | 88 |

|            | Circuit design parameters for the 2-stage doubler in Figure 6.14 (2.2 Volt supply)  |    |

|            | Circuit design parameters for the frequency halver in Figure 6.17 (2.2 Volt supply) |    |

|            | Summary of the simulated LO system performance.                                     |    |

|            | Measured LO system performance.                                                     |    |

|            | Measured Receiver Performance and Benchmark Comparison                              |    |

|            |                                                                                     |    |

# **List of Figures**

| Figure 2.1: Single-conversion superheterodyne AM-receiver block diagram                          | 14  |

|--------------------------------------------------------------------------------------------------|-----|

| Figure 2.2: Frequency spectrum showing a double sideband (DSB) down-conversion.                  |     |

| Figure 2.3: Conventional integrated heterodyne receiver front-end.                               | 15  |

| Figure 2.4: Image reject mixer topology and rejection.                                           |     |

| Figure 2.5: Receiver IC block diagram.                                                           |     |

| Figure 2.6: Internal schematic view of the receiver front-end.                                   |     |

| Figure 2.7: Oscillator tank resonator and feedback network                                       |     |

| Figure 2.8: Small signal performance of a minimum-size NT25 device.                              |     |

| Figure 2.9: Unity gain frequency (fT) versus IC for a "nominal" device with VCE = 1V.            |     |

| Figure 2.10: Magnitude of the small-signal ac current gain versus frequency                      |     |

| Figure 2.11: Typical CMOS quadrature LC oscillator[27].                                          | 21  |

| Figure 2.11. Typical CiviOs quadrature DC oscillator[27]                                         | غال |

| Figure 2.12: Polyphase filter (2-stage)                                                          |     |

|                                                                                                  |     |

| Figure 2.14: Scaled-emitter Gilbert quad multiplier.                                             | 32  |

| Figure 2.15: Transformer based frequency doubler.                                                |     |

| Figure 2.16: Resonator based frequency multiplier.                                               |     |

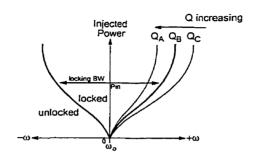

| Figure 3.1: Phase of an injection locked oscillator versus the relative injected frequency[37]   |     |

| Figure 3.2: Injection locked oscillator model.                                                   |     |

| Figure 3.3: Typical locking range of an ILO.                                                     |     |

| Figure 3.4: Injection locked ring oscillator topology.                                           | 42  |

| Figure 3.5: Simulink model of the ring oscillator in Figure 3.4.                                 | 44  |

| Figure 3.6: Oscillator Amplitude - HSPICE vs. Simulink.                                          |     |

| Figure 3.7: Locking range - HSPICE vs. Simulink.                                                 |     |

| Figure 3.8: An ILRO model using a three-pole amplifier model.                                    |     |

| Figure 3.9: Differential amplifier phase shift.                                                  |     |

| Figure 3.10: Graphical representation of equation 3.21.                                          |     |

| Figure 4.1: Regenerative doubler block diagram.                                                  |     |

| Figure 4.2: Regenerative doubler simplified schematic diagram.                                   |     |

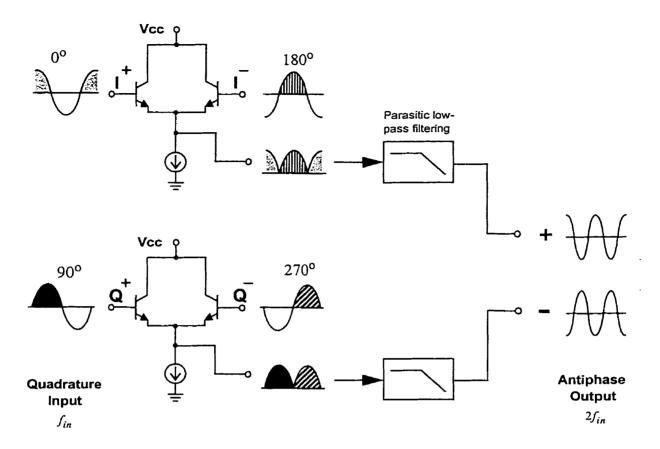

| Figure 4.3: Illustration of quadrature input to differential output in the ring amplifiers.      |     |

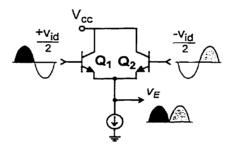

| Figure 4.4: Emitter-coupled pair driven in a large-signal model.                                 |     |

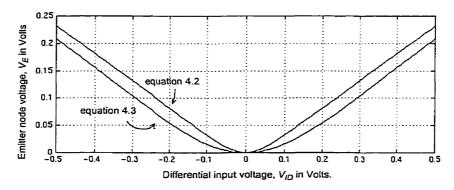

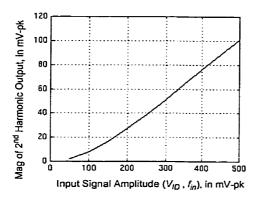

| Figure 4.5: Emitter-coupled node voltage as a function of differential input voltage             |     |

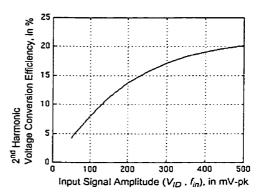

| Figure 4.6: Voltage conversion.                                                                  |     |

| Figure 4.7: Regenerative frequency quadrupler                                                    |     |

| Figure 4.8: Regenerative frequency tripler.                                                      |     |

| Figure 4.9: A frequency-tracking injection locked ring oscillator.                               |     |

| Figure 5.1: 2-Stage frequency halver block diagram.                                              |     |

| Figure 5.2: Simulink model of the 2-stage regenerative divider.                                  | 69  |

| Figure 5.3: Regenerative divider simplified schematic diagram.                                   |     |

| Figure 6.1: Local oscillator subsystem architecture.                                             | 72  |

| Figure 6.2: General buffer topology.                                                             | 73  |

| Figure 6.3: Planar Illustration of the emitter window layout and etched areas[44]                |     |

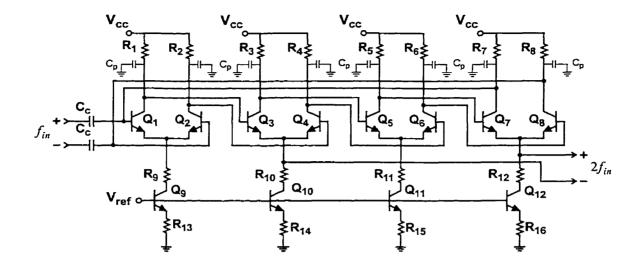

| Figure 6.4: 4-Stage ring: (first) frequency doubler.                                             |     |

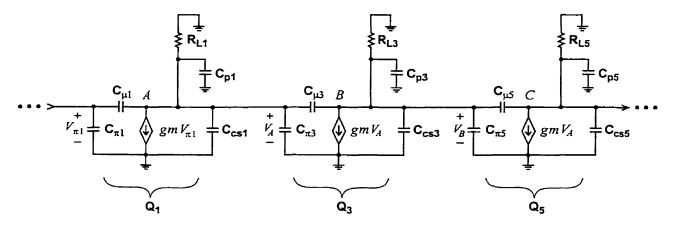

| Figure 6.5: AC small-signal half-circuit of an amplifying stage in the ring.                     |     |

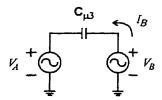

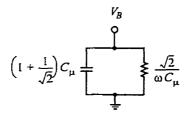

| Figure 6.6: Calculating the admittance looking into Cm3 from node B                              | 78  |

| Figure 6.7: Shunt RC equivalent network of Cm3 from the viewpoint of node VB                     | 79  |

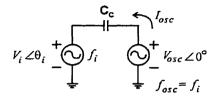

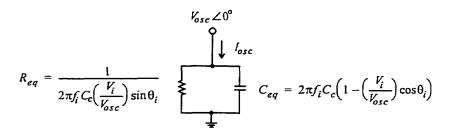

| Figure 6.8: Half-circuit showing input signal injection source (Vin) and coupling capacitor (Cc) | 82  |

| Figure 6.9: Injected signal Vi coupled to the locked oscillator.                                 | 83  |

| Figure 6.10: Equivalent injection loading network as seen by the oscillator                      | 84  |

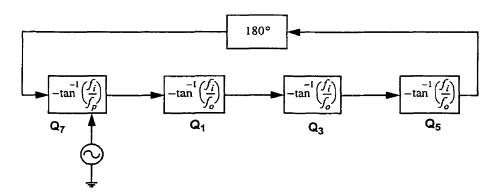

| Figure 6.11: Injection locked oscillator phase delays (half-circuit view).                       | 84  |

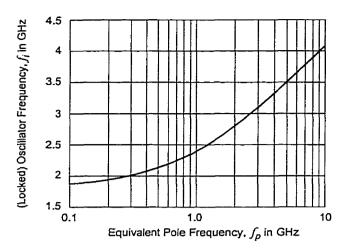

| Figure 6.12: Oscillator frequency as a function of the equivalent pole frequency fp              | 86  |

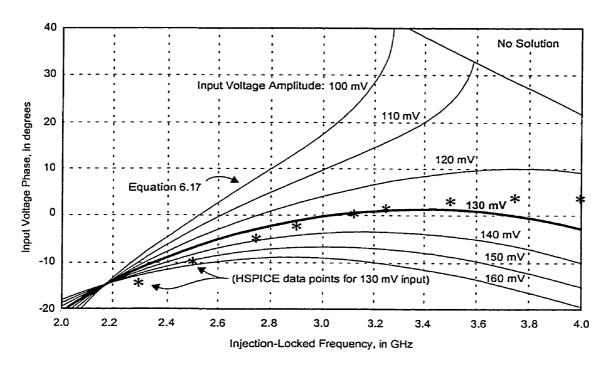

| Figure 6.13: Input voltage phase versus frequency for various input amplitudes                   | 87  |

#### List of Figures

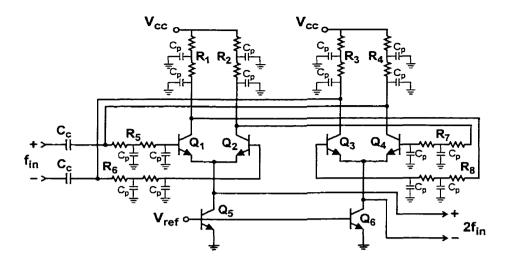

| Figure 6.14: 2-stage ring: (second) frequency doubler                                           | 89 |

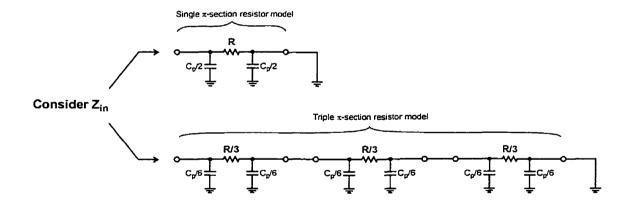

|-------------------------------------------------------------------------------------------------|----|

| Figure 6.15: Single versus triple p-section resistor model                                      |    |

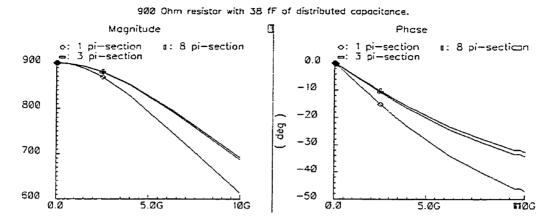

| Figure 6.16: Comparison of a 1, 3, and 8 p-sectioned resistor model for a 900 Ohm, 38fF layout. | 90 |

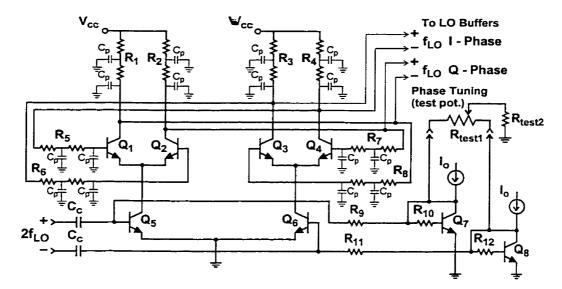

| Figure 6.17: 2-Stage Ring: Frequency Halver / I-Q Signal Generator with Phase Tuning            | 93 |

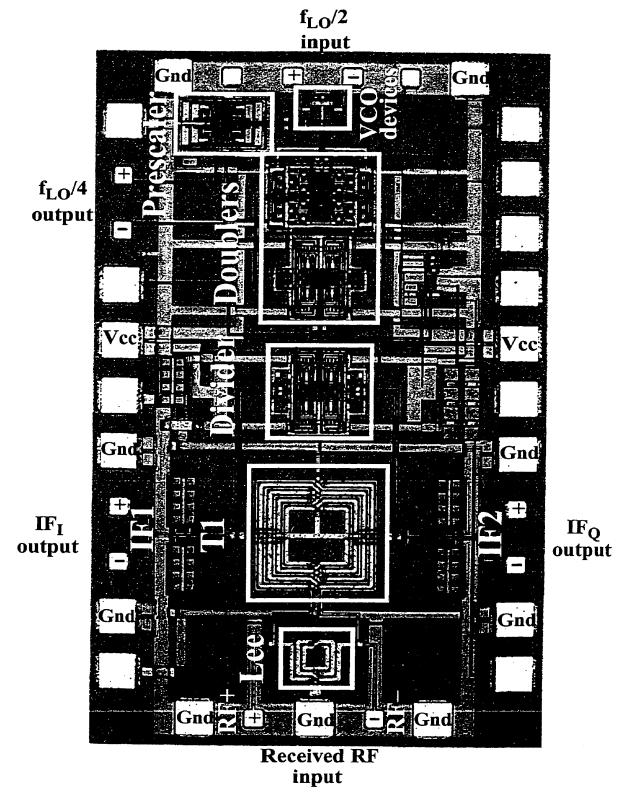

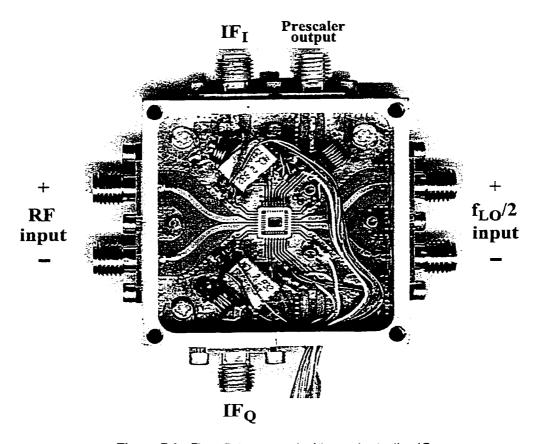

| Figure 7.1: Photo-micrograph of the 5-6GHz receiver IC with regenerative LO system              | 97 |

| Figure 7.2: Test fixture created to evaluate the IC.                                            | 98 |

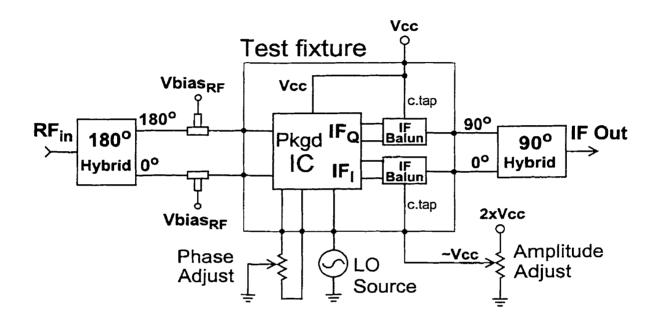

| Figure 7.3: Test setup block diagram                                                            | 99 |

| Figure 7.4: SSB phase noise of the prescaler output.                                            |    |

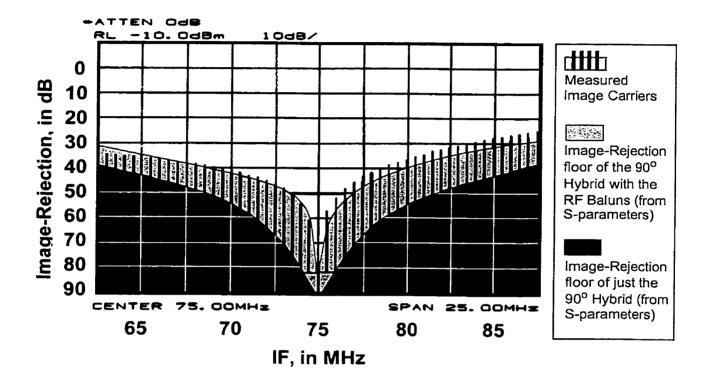

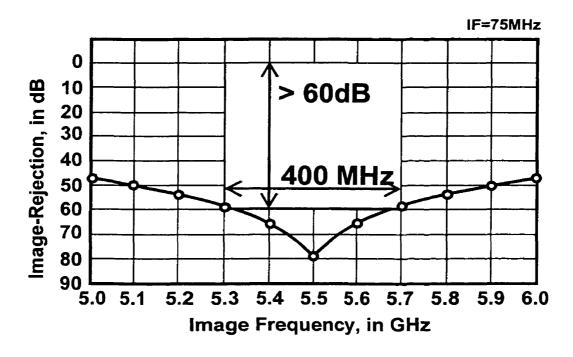

| Figure 7.5: Wideband image rejection using a discrete quadrature hybrid                         |    |

| Figure 7.6: RF-LO sweep test.                                                                   |    |

| Figure A.1: Basic oscillator circuit                                                            |    |

| Figure A.2 Vector diagram of instantaneous voltages                                             |    |

| Figure A.3 Phase versus frequency for a simple tuned circuit                                    |    |

# CHAPTER 1

# Introduction

#### 1.1 Introduction

The success of cellular telephony and the internet has lead to growing consumer demand for wireless connectivity, products, and services. Although the vast majority of this growth so far has been in mobile voice telephony applications, there is increasing interest in low-rate wireless data applications such as message services or wireless e-mail to consumers[1]. Significant advancements in the area of radio-frequency integrated circuit (RFIC) technology are required to achieve the power, performance, cost and size requirements for these next-generation wireless applications.

In this thesis, new RF circuit techniques are presented which enable an increased level of system integration in an integrated receiver by providing a means of frequency multiplication and precise phase quadrature signal generation. The phase accuracy of the quadrature signals realized enables a Hartley-type downconverter to achieve an image rejection that is sufficient to eliminate the requirement for external (discrete) RF filters in the first RF stage of a recever. This allows for a simpler package and increased design flexibility without sacrificing significant receiver performance. These techniques are demonstrated in a test receiver IC in the 5-6 GHz band as this is an area of increasing commercial interest for broadband wireless data communications.

Chapter 1: Introduction 11

## 1.2 Next Generation Wireless LAN

Over the last five years, the unlicensed 900MHz ISM (instrument, scientific and medical) band (13MHz of spectrum) has become completely saturated in many urban centers by lowend applications such as cordless phones, cheap analog extensions, remote control devices, etc. In anticipation of this congestion, the 2.4 GHz ISM band (which has roughly 83 MHz of spectrum) is considered as an up-banded alternative for WLAN applications. However, the ISM band at 2.4GHz is insufficient for the anticipated level of activity in WLAN, although it is available worldwide. In the late 90's, 300-500 MHz of licence-exempt spectrum in the 5-6GHz band was allocated in many regions[2,3], which can be used for both fixed and portable wireless multimedia applications at data-rates between 20 and 150 Mb/s.

# 1.2.1 Frequency Specifications and System Design Challenges

| Standard                | Bluetooth                      | HomeRF                              | IEEE 802.11b<br>FH                   | IEEE 802.11b<br>DS-SS | HIPERLAN             | IEEE 802.11a<br>UN-II                       | HIPERLAN/2                                  |

|-------------------------|--------------------------------|-------------------------------------|--------------------------------------|-----------------------|----------------------|---------------------------------------------|---------------------------------------------|

| Frequency<br>allocation | 2.402 -2.480<br>GHz            | 2.404 -2.478<br>GHz                 | 2.400 -2.4835<br>GHz                 | 2.400 -2.4835<br>GHz  | 5.15-5.35 GHz        | 5.150-5.350 and<br>5.725-5.825 GHz          | 5.150-5.350 and<br>5.425-5.725 GHz          |

| Total spectrum          | 78 MHz                         | 74 MHz                              | 83.5 MHz                             | 83.5 MHz              | 200 MHz              | 300 MHz                                     | 500 MHz                                     |

| Modulation scheme       | FHSS-<br>1600hops/sec,<br>GFSK | FHSS-<br>50hops/sec,<br>FSK & 4-FSk | FHSS-vari-<br>able, 2-FSK,<br>4-FSK, | BPSK, QPSK            | Differential<br>GMSK | OFDM 52-car.<br>BPSK,QPSK,<br>16QAM, 64QAM. | OFDM 52-car.<br>BPSK,QPSK,<br>16QAM, 64QAM. |

| Peak raw<br>data-rate   | 0.721 Mbps                     | 0.8 and 1.6<br>Mbps                 | l and 2 Mbps                         | 11 Mbps               | 23.5 Mbps            | 54 Mbps (increase proposed)                 | 54 Mbps (increase proposed)                 |

| RF channel<br>bandwidth | l MHz                          | 1 MHz                               | l MHz                                | 22MHz                 | 23.5 MHz             | 20 MHz                                      | 20 MHz                                      |

Table 1.1 Comparison of various WLAN standards [4,2,3]

Table 1.1 compares the key physical-layer attributes for some of the more popular WLAN standards in order of increasing data-rate from left to right. Although the 802.11b standard enables a rate of 11 Mbps (competitive with the Ethernet rate of 10 Mbps), there is a growing movement to use the 2.4GHz band exclusively for sub-1 Mbps applications due to the limited total channel capacity (limited by the 83.5MHz spectral width available). Wireless computer peripheral devices that are supported by Bluetooth and HomeRF standards, add more electromagnetic clutter to the 2.4 GHz band and motivate migration to the 5-6GHz band for Mbps WLAN.

Chapter 1: Introduction 12

One of the challenges faced by RFIC designers of next generation WLAN equipment, is the doubling of operating frequency and increase in bandwidth compared to the previous (2.4GHz) generation. Power consumption is always an important consideration in portable applications, and a significant increase in bias current for the RF circuits (for a given technology) can be expected as the frequency of operation is doubled due to the relationship between device bandwidth and supply current. New low-voltage topologies are therefore needed to keep the overall power dissipation down and maintain supply compatibility between analog and digital circuit blocks. Also, tuning range is arguably one of the most important considerations for architects of a 5-6 GHz receiver.

According to the IEEE 802.11a standard, the frequency allocations for unlicensed operation in North America (UN-II) have been split into two bands: 5.15-5.35GHz and 5.725-5.825GHz[2]. In Europe however, the HIPERLAN/2 standard shares the lower band with UN-II but specifies the upper band at 5.47-5.725GHz[3]. Other non-WLAN potential applications lie in the 5.8-5.9GHz region where international allocations have been made for intelligent transportation system services using dedicated short-range communications[5]. Unlike the spectral allocations for cellular telephony, the specific frequency plan (including the uplink and downlink splits) within the unlicensed band can be determined arbitrarily by the applications engineer. A 1 GHz tuning range, centered at 5.5 GHz, represents a 20% relative bandwidth or tuning ratio, which is significantly larger than the 3% requirement at 2.4 GHz. Although none of the 5-6GHz WLAN standards currently require the receiver (or transmitter) to tune over the entire band, the lack of a unified global standard encourages the design of a wideband generic IC in order to broaden the scope of its application.

At the time of writing, two commercial solutions have appeared on the market for the 802.11b standard[6][7]. Both are highly integrated, two-chip solutions implementing both RF and baseband functions in standard CMOS processes.

# 1.3 Organization of this thesis

Chapter 2 of this thesis begins with a general discussion of the heterodyne and imagereject receiver architectures, followed by an overview of the process technology and a description of the 5-6 GHz receiver testchip. One of the main goals of this work is to enable an increased level of integration in a receiver by eliminating the need for an off-chip image-reject filter in the RF front-end. The challenges and benefits involved in replacing this filter are discussed in detail, and an integrated receiver concept is presented to accomplish this.

The main focus of this work is on the generation of a pair of highly-accurate quadrature-phase-shifted local oscillator signals at 5-6 GHz. Injection locked oscillators are employed in the design and enable a new method of frequency doubling on an IC. The underlying concept of an injection-locked oscillator is studied and then extended to the locking of ring-type oscillators. Hand analysis and Simulink models are used to illustrate the key characteristics of the injection-locked ring-oscillator. Injection-locking techniques are exploited in both frequency-doubling and dividing circuits to generate local oscillator signals for the receiver. The multi-oscillator system employed in the IC is presented along with the schematics of the individual oscillators and a full discussion of their operation. The thesis is concluded with an overview of the test setup and a discussion of the measured results.

# The Local Oscillator

# **System**

This chapter begins with a review of superheterodyne and image-reject receiver architectures, followed by a block-level description of the test-receiver IC characterized in this work. The portion of the receiver referred to as the "local oscillator system" is defined, and a breakdown of its requirements and design specifications is given. The process technology used to fabricate the IC is also presented and discussed briefly within the context of a 5-6 GHz receiver.

Frequency doubling is an important part of the contribution of this thesis and so a background review of some of the current methods of frequency doubling on an IC is covered at the end of the chapter.

# 2.1 The Basic Superheterodyne Receiver

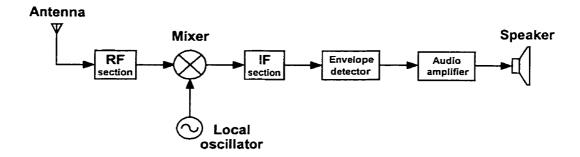

The superheterodyne receiver is one of the most common receiver topologies employed in radio communication systems today. Invented by Edwin Armstrong in the early 1900's, the basic structure is illustrated in Figure 2.1. This block diagram shows an example of the heterodyne concept applied to an AM (amplitude-modulated) broadcast-band application.

Figure 2.1: Single-conversion superheterodyne AM-receiver block diagram.

The general requirements of a receiver include: the ability to select the desired RF signal (or station) through carrier-frequency tuning, filtering out unwanted or adjacent channels, as well as amplifying the desired signal. In addition to these requirements, the information contained in the received signal must be extracted (i.e. demodulated). In the case of the AM-radio example, the received radio waves from the distant station are converted to audible sounds at the speaker.

Beginning at the left of the diagram, RF waves are picked up by the antenna and fed to the input of the receiver. The RF section typically provides signal amplification as well as some bandpass filtering. In an AM broadcast-band radio, the RF section is designed to amplify signals from 535KHz to 1600KHz and to also reject signals at frequencies which are outside of this band.

The local oscillator (LO) block generates a constant envelope (or non-modulated) carrier-wave (CW) signal which is multiplied with the received RF signal in the mixer. The result of the multiplication is a double-frequency translation of the input signal, up and down in frequency, by the LO. This multiplication can be expressed by the equation,

$$A_m(t)\cos(2\pi f_{RF}\,t + \phi_m(t)) \cdot \cos(2\pi f_{LO}\,t) = \frac{A_m(t)}{2} \left[\cos(2\pi (f_{RF}\,+f_{LO})\,t + \phi_m(t)) + \cos(2\pi (f_{RF}\,-f_{LO})\,t + \phi_m(t))\right], (2.1)$$

where  $A_m(t)$ ,  $\phi_m(t)$ , and  $f_{RF}$  represent the amplitude modulation, phase modulation, and frequency of the input RF carrier, and where  $f_{LO}$  represents the frequency of the LO. From the right side of equation 2.1, it can be seen that the RF input signal is converted from  $f_{RF}$  to a pair of signals found at  $f_{RF} + f_{LO}$  and  $f_{RF} - f_{LO}$  at the output of the mixer. Also,

amplitude and phase modulation of the original signal is preserved in the translated outputs. The use of frequency translation (or frequency conversion) in this way is heterodyning.

In the receiver of Figure 2.1, the desired RF signal is down-converted by the LO to a lower, fixed intermediate frequency (or IF). By adjusting the frequency of the LO, the frequency of the signal being received is "tuned" to fall into the chosen IF band,

$$f_{RF} - f_{LO} = f_{IF} . {(2.2)}$$

In the IF section, the received signal is amplified and passed through a fixed-frequency channel-select filter. This filter is designed to suppress both adjacent as well as out-of-band signals, and provides frequency selectivity in receiver. The width of the passband of the channel-select filter is determined primarily by the channel spacing and modulation characteristics of the signals being received.

The IF is usually chosen to be much lower in frequency than the signals being received in order to realize a number of practical advantages, such as: increased efficiency in the amplifying devices, a reduction of unwanted parasitics, and a relaxed relative bandwidth (  $\Delta f/f_o$  ) requirement for the channel-select filters. Consider for example, a receiver which is designed to receive a 100KHz channel at 1 GHz. If channel-select filtering is implemented directly at RF, then a filter with a 0.01% relative bandwidth would be necessary. This is an extremely difficult specification to meet at 1GHz with current filtering technology[8]. A single-pole RLC filter for example, requires a resonator quality factor on the order of 10,000 (i.e., 1/relative bandwidth)[9]. Implementing the channel-select filtering directly at the IF is an alternative. Consider the same passband filtering requirement when implemented in the IF section, after translating the received 1GHz signal down to an IF of 1MHz. The relative bandwidth is now 10% and the Q-factor requirement for the resonator has been reduced to 10. This relative-bandwidth parameter flexibility is one of the key reasons why the heterodyne architecture is so popular.

The circuit blocks in Figure 2.1 to the right of the IF section complete the AM receiver. All of the blocks lying in the path of the received signal from the IF section to the end of the receiver, are collectively known as the "back-end" of the radio. The back-end in Figure 2.1 is capable of receiving and demodulating AM signals at the IF and is essentially a fixed-

frequency receiver. Conversely, the "front-end" of the radio is everything in the receive path prior to the IF and is in essence a frequency converter. It should be noted however, that the LO generator (or synthesizer) is not in the direct path of the received signal and is therefore not included as part of the front-end.

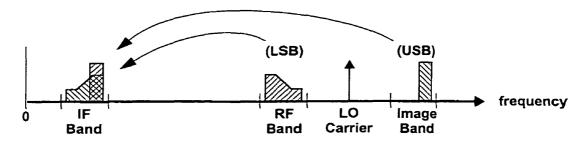

# 2.2 The Image band in a Heterodyne Receiver

In equation 2.1, the process of mixing the LO with the RF was shown to generate two products, one at the sum of the LO and RF frequencies (referred to as the upconversion) and one at the difference between them (downconversion). The upconversion term can be ignored since it is filtered away in the IF section, leaving only the downconversion term,

$$x_{IF}(t) = \frac{A_m(t)}{2} \cos(2\pi (f_{RF} - f_{LO}) t + \phi_m(t)) . \qquad (2.3)$$

Equation 2.3 is appropriate in situations where the frequency of the RF signal being considered is above the frequency of the LO. Since a cosinusoid is an even function of time, equation 2.3 can also be written as

$$x_{IF}(t) = \frac{A_m(t)}{2} \cos(2\pi (f_{LO} - f_{RF}) t - \phi_m(t))$$

(2.4)

if the frequency of the RF signal is below the frequency of the LO. From equations 2.3 and 2.4, the RF signal frequencies which will be converted to a specific IF for a given LO frequency are

$$f_{RF} = f_{LO} \pm f_{IF} \ . \tag{2.5}$$

This means that for a 500MHz LO and a 10MHz IF, a mixer will convert RF signals received at both 510MHz and 490MHz to the IF. The RF band located above the LO is referred to as the upper sideband (or USB) whereas the RF band below the LO is referred to as the lower sideband (or LSB). In many applications, only one of the sidebands is desired. The unwanted part of RF spectrum which converts to the IF is commonly referred to as the "image" band. This is illustrated in Figure 2.2 for the case where the LSB is the desired RF band to be received.

Figure 2.2: Frequency spectrum showing a double sideband (DSB) down-conversion.

The image band in a receiver is normally filtered out before mixing so that only the desired (RF) band is converted to the IF. The amount of image band suppression (or image rejection) in a receiver is an important receiver performance specification. In high-end wireless applications, a total image rejection (IR) on the order of 70-100dB is typically required[10].

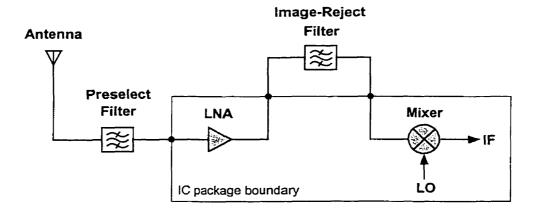

# 2.3 Filtering out the Image Band

Figure 2.3 illustrates a common heterodyne front-end employed in many receiver designs to reject the image.

Figure 2.3: Conventional integrated heterodyne receiver front-end.

The RF input signal at the antenna passes through a preselect filter which band-limits the input of the receiver to prevent out-of-band carriers from desensitizing or overloading the low-noise amplifier (or LNA). In situations where the image band can be designed to fall

outside of the passband of this filter, an image rejection on the order of 20dB is realized. The stopband attenuation of this filter is typically limited by the amount of insertion loss that can be tolerated at the input of the receiver, as this adds directly to the overall noise figure of the system[11]. The bulk of the image rejection in an integrated application is usually provided by a second off-chip filter placed between the LNA and mixer. This IR filter is typically more aggressive than the preselect filter (~ 45dB), and has a higher insertion loss (~3-4dB). The noise introduced by the this second filter is acceptable since it is suppressed by the gain of the LNA[11].

A common design strategy employed in tandem with this filtering arrangement is to use a multiple frequency-conversion scheme so that the RIF and image band are widely separated (which relaxed the image filtering requirements), while subsequent IFs are chosen to be much lower in frequency to relax the relative bandwidth requirements for channel selection filtering or to suit A/D conversion requirements.

This front-end topology works well in many low-cost integrated circuit packages up to the 2-3GHz range[12,13,14]. In the 5-6GHz range however, receiver performance is unnecessarily compromised by having to route R:F signals through off-chip filtering components. Wideband impedance matching networks required to match the on-chip LNA and mixer to the external filter introduce loss. Also, undesired mutual coupling across bond wires of the package and among the printed circunit board lines also degrade receiver performance. Multi-chip modules with controlled impedance packages reduce parasitics and losses but not power consumption and add significant cost. Furthermore, fixed-frequency discrete RF filters limit system flexibility in an open stændard environment.

# 2.4 Image-Reject Mixing

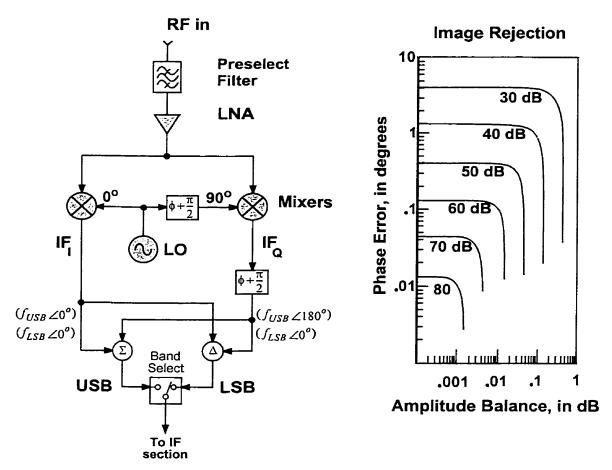

- a) Hartley receiver downconverter

- b) image rejection vs. amplitude and phase errors in quadrature signals

Figure 2.4: Image reject mixer topology and rejection.

An alternative frequency-conversion architecture which also rejects the image band at the IF is the Hartley image-reject mixer [15] illustrated in Figure 2.4a. Here, the RF input is split into two paths and downconverted by a quadrature (or  $90^{\circ}$  phase shifted) pair of LO signals into an IF<sub>I</sub> (in-phase) and an IF<sub>Q</sub> (quadrature) path.

The frequency conversion of the input RF to the  $IF_I$  path has already been expressed by equations 2.3 and 2.4. The signals which appear at the  $IF_Q$  node can also be determined in a similar way. In the quadrature path, the RF and LO multiplication can be expressed as,

$$A_m(t)\cos(2\pi f_{RF}t + \phi_m(t)) \cdot \sin(2\pi f_{LO}t) = \frac{A_m(t)}{2} \left[\sin(2\pi (f_{RF} + f_{LO})t + \phi_m(t)) + \sin(2\pi (f_{LO} - f_{RF})t - \phi_m(t))\right] \quad .(2.6)$$

The upconversion term  $(f_{RF} + f_{LO})$  can be dropped (as it is filtered out in the IF), and the IF<sub>Q</sub> signal can be expressed for LSB RF signals as,

$$IF_{Q}(t) = \frac{A_{m}(t)}{2}\sin(2\pi(f_{LO} - f_{LSB})t - \phi_{m}(t)), \qquad (2.7)$$

(where  $f_{LSB} = f_{RF}$  for  $f_{RF} < f_{LO}$ ). Since a sinusoid is an odd-symmetric function of time, RF signals above the frequency of the LO (i.e.,  $f_{USB}$ ), will appear in the IF with a polarity reversal,

$$IF_{Q}(t) = (-1)\frac{A_{m}(t)}{2}\sin(2\pi(f_{USB} - f_{LO})t + \phi_{m}(t)).$$

(2.8)

The  $\frac{\pi}{2}$  phase shift block in the IF<sub>Q</sub> path effectively converts the sine functions in equations 2.7 and 2.8 into cosine functions so that the USB and LSB signals in the I and Q paths will have the phase relations as noted in parentheses on Figure 2.4a. When the two IF paths are summed, the LSB signals are (ideally) anti-phase and cancel out leaving only the USB remaining in the IF output. When the difference element is selected however, the opposite occurs and (ideally) only LSB signals remain.

In practice there are many parasitic sources of error which can degrade the receiver's image-reject performance. Any gain or quadrature phase errors between the I and Q-LO signals or between the  $IF_I$  and  $IF_Q$  signal paths, degrades the rejection of the undesired sideband at the output. The image rejection obtained can be expressed in dB as,

$$IR(\theta_{e}, G) = -10\log\left[\frac{1 - 2\sqrt{G}\cos(\theta_{e}) + G}{1 + 2\sqrt{G}\cos(\theta_{e}) + G}\right]. \tag{2.9}$$

where  $\theta_e$  is the overall phase error from quadrature and G is the total gain imbalance factor between the IF<sub>I</sub> and IF<sub>Q</sub> signals[16]. The amplitude imbalance in dB is related to the gain imbalance factor by

$$A = 10\log G. \tag{2.10}$$

Figure 2.4b shows a plot of the image rejection calculated as a function of the total phase and amplitude error. In order to achieve an image rejection on the order of 40-50dB (and thus eliminate the need for off-chip image filtering), a total system phase error of less than 1° is necessary (given an amplitude imbalance < 0.1 dB).

#### 2.5 5-6 GHz Receiver Architecture

In a 5-6GHz integrated receiver application, the image-reject receiver topology is desirable as since it does away with the need for discrete filtering at the RF. This enables the use of a lower cost RF package and achieves a higher level of system integration. In order to use the image-reject mixing technique, a means of generating accurate on-chip quadrature LO signals in the 5-6GHz range is required. In this thesis, new circuit techniques are developed which provide an efficient means of generating low-noise quadrature LO signals on-chip from a lower-frequency external source or tank resonator. In order to verify the performance of these techniques, a 5-6GHz image-reject test receiver was fabricated in a silicon-bipolar technology with 0.5 micron minimum feature size and a unity gain frequency ( $f_T$ ) of 25 GHz[17].

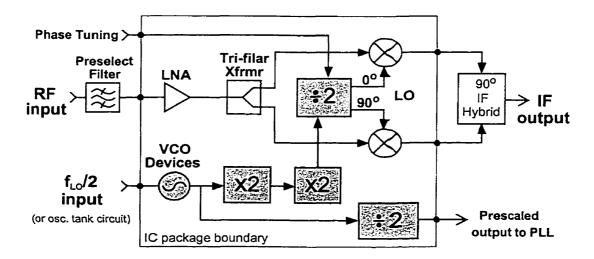

Figure 2.5: Receiver IC block diagram.

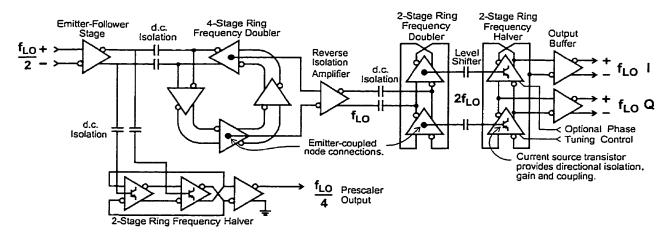

Figure 2.5 shows a block diagram of the test receiver IC and supporting circuitry. The circuits presented in this thesis are identified by the shaded blocks in the diagram and are

collectively referred to as the "LO system". The LO system includes the active devices for a voltage-controlled oscillator (VCO), a cascaded pair of regenerative frequency-doubling stages, a regenerative quadrature divider with phase control, and an analog divide-by-2 prescaler. The image-reject receiver front-end (unshaded blocks in the IC) were first presented in [18].

#### 2.5.1 Overview of the Receiver Front-End

Balanced differential circuitry is used throughout the IC to reduce signal injection into the substrate and to help reduce crosstalk by minimizing stray ground currents. This doubles the power consumption in many of the blocks compared to single-ended realizations and therefore low-voltage operation is emphasized throughout the IC.

Referring to Figure 2.5, the RF input signal first passes through an off-chip preselect filter and then enters the IC. Package parasitics at this transition are absorbed in the design of the LNA's input matching network. An integrated three filament transformer is used to both split and couple the output of the LNA to the inputs of the I and Q mixers. The mixer LO ports are driven by a quadrature divide-by-2 stage in the LO system, and the converted outputs are taken off-chip and recombined in a discrete IF quadrature combiner (e.g., 90° hybrid).

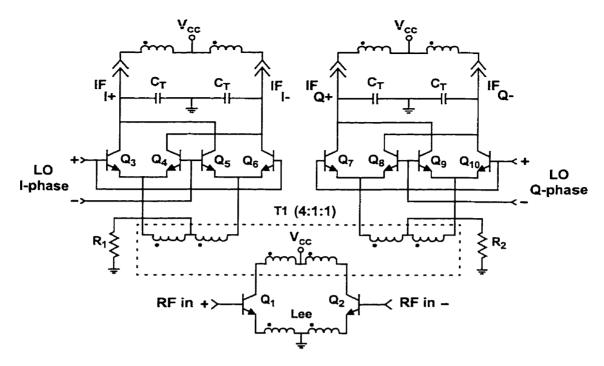

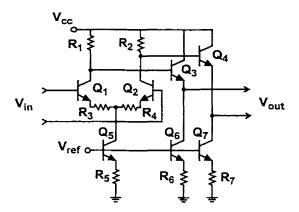

Illustrated in Figure 2.6 is a schematic diagram of the test-receiver's front-end designed by Long[19]. The LNA is formed by  $Q_I$  and  $Q_2$  and has emitter degeneration inductance  $L_{ee}$  to improve matching and linearity of the stage. A 4:1:1 turns-ratio integrated transformer,  $T_I$  provides both impedance matching and differential coupling between the high impedance output of the LNA and the low impedance inputs of the mixer quads. Discrete off-chip transformer baluns are used to bias the collector nodes of the mixers and to impedance match the output to 50 ohms. The base-node inputs of the I and Q mixer-quad transistors ( $Q_3$ - $Q_6$  and  $Q_7$ - $Q_{10}$ ), are driven by quadrature LO signals generated by the LO system. The transformer allows for separate biasing of the LNA and mixers. The front-end can operate from a 0.9 V supply without significant performance degradation.

Figure 2.6: Internal schematic view of the receiver front-end.

# 2.6 LO System Overview

Referring again to Figure 2.5, the primary function of the LO system (identified by the shaded blocks), is to generate a low phase noise, accurate, quadrature LO pair of differential signals to drive the I and Q mixers. The external LO source is multiplied by a factor of four through a cascade of frequency doublers ("X2" stages) and then divided-by-two in order to generate an accurate quadrature pair of LO signals internally at twice the external source frequency. A divide-by-2 frequency prescaler is also included on the IC to allow easy compatibility with low-cost, sub-2GHz PLL synthesizer ICs.

In the image reject mixer architecture, the second 90° phase shift required at IF is one of the most difficult functions to realize. In the test setup for this receiver, this phase shift is carried out off-chip by a discrete component. Ideally this phase shift should be constant over the required bandwidth (which can be as wide as 50MHz in a 5GHz application), highly linear, and of relatively low loss. Although a digital implementation is possible, it is very advantageous to perform this function in the analog domain (preferably using passive

networks) so that any large interferers in the image band can be cancelled out prior to digitalization where spurious components can be generated in the IF. This significantly eases the linearity requirements for the receiver's A/D converter.

A systematic offset error (as small as 2°) in any part of the I-Q signal path will seriously degrade the overall image rejection (as observed in the curves of Figure 2.4b). One option is to cancel out any phase error at IF by providing an equal and opposite phase shift in the quadrature LO signals. Included in Figure 2.5, is a dc-input "phase control" line to the IC which provides a means for precisely adjusting the phases of the I and Q LO signals.

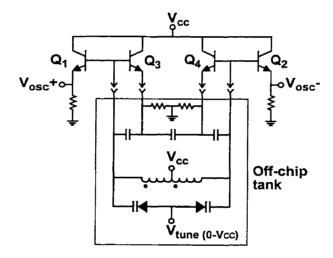

Also shown in the block diagram is an oscillator symbol labeled "VCO devices". The LO system is designed to allow either an external signal source or tank resonator to be used with the IC. A possible differential tank structure is illustrated in Figure 2.7.

Figure 2.7: Oscillator tank resonator and feedback network

Using the active devices available on the IC and a minimum number of external components (found in the shaded region), a voltage-controlled Colpitts-type oscillator can be implemented [20].

# 2.7 IC Fabrication Technology Overview

Nortel's 25GHz  $f_T$  self-aligned double-poly silicon bipolar technology (NT25) was used for the test-chip implementation. The NT25 process has three layers of aluminum metallization with a 2 $\mu$ m thick top metal, a 1 fF/ $\mu$ m<sup>2</sup> capacitor dielectric layer, and polysilicon resistors. The NT25 design kit also includes fully-scalable HSPICE and Spectre RF simulation models as well as the corresponding device physical layouts.

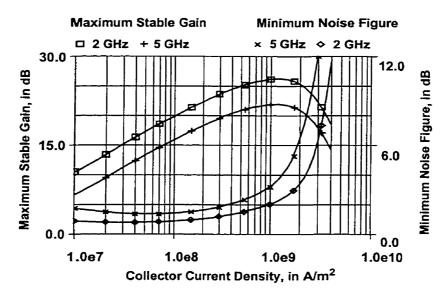

Figure 2.8: Small signal performance of a minimum-size NT25 device.

Shown in Figure 2.8 is the maximum stable gain and minimum noise figure for a 0.5µm x 2.5µm emitter area device. The overall conversion gain targeted for the front-end of the receiver is 15dB, and it can be seen that at a collector current density of 3.5e8 A/m<sup>2</sup>, a 2dB noise figure(NF) and a maximum stable gain (Gmax) of 20dB is achievable.

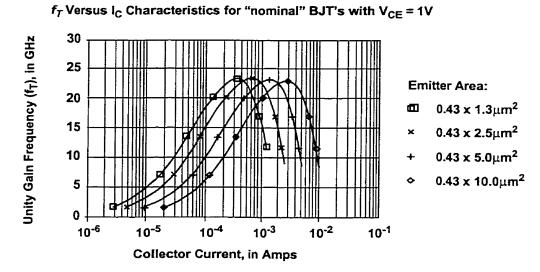

Figure 2.9 plots the unity current-gain frequency  $(f_T)$  as a function of the collector current for various transistor sizes[21]. From the above plotted data it can be seen for example, that a collector current of approximately 1.5mA is required for maximum  $f_T$  biasing of a 0.43 x 5.0 $\mu$ m<sup>2</sup> emitter area device.

Figure 2.9: Unity gain frequency ( $f_T$ ) versus  $I_C$  for a "nominal" device with  $V_{CE} = 1V$ .

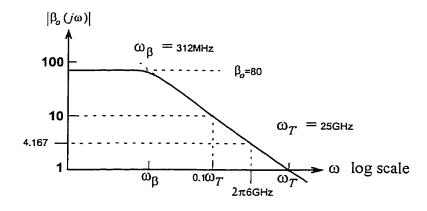

The magnitude of the small-signal ac current gain of a bipolar transistor ( $|\beta_o(j\omega)|$ ) above the cut-off frequency can be approximated as,

$$\omega_T = \omega_x |\beta_o(j\omega)| \tag{2.11}$$

where  $\omega_T$  is the unity gain frequency of the transistor and  $\omega_x$  is the operating frequency[22]. This relation is plotted in Figure 2.10 for a typical transistor available in the NT25 technology.

Figure 2.10: Magnitude of the small-signal ac current gain  $|\beta_{\sigma}(j\omega)|$  versus frequency

This implies that many of the devices must be biased near maximum  $f_T$  due to the low current gain available in the 5-6GHz range. Careful transistor bias optimization is required in order to keep power dissipation low.

# 2.8 LO System Operating/Design Requirements

Specification **Design Target** Minimum voltage <u>2</u>V Total IC power dissipation target < 50mW < 25mW LO system power dissipation Receiver operating range 5-6GHz Intermediate frequency range DC-500MHz 4.5GHz-6.5GHz LO output frequency range (i.e.,  $f_{RF} \pm f_{IF}$ ) Image Rejection Target >45 dBLO quadrature phase accuracy < 1° LO I and Q amplitude balance < 0.1 dB

Table 2.1 LO system design, target specifications.

Table 2.1 describes the overall requirements for the design of the LO system. A 2-volt supply is targeted in order to reduce power consumption in the receiver and to maintain compatibility with signal processing circuits that will likely be implemented in deep sub-micron CMOS technologies. A total power dissipation of less than 50mW is desired for the entire receiver, of which half is allocated to the LO system.

Although the front-end topology has been presented in the context of an image-reject architecture, it can just as easily be employed in a direct conversion design. In a direct conversion receiver, the RF is converted directly to baseband or zero-IF[23]. In this configuration, the LO system must be capable of operating over the entire 5-6GHz range. Furthermore, to maximize system flexibility, the IC should support the image-reject architecture with either high-side or low-side injection over the entire band without the need for switching sidebands half way. This implies that in order to support an IF of up to 500MHz, the operating range of the LO system must be at least 4.5-6.5GHz. A 500MHz IF capability is

targeted for the design. The motivation for supporting such a high first IF in an image-reject architecture is that if the 90° quadrature combiner is realized using a passive network, a higher IF reduces the fractional bandwidth ( $\Delta f/f_{IF}$ ) over which the hybrid must maintain a constant 90° phase shift. This eases the design of the hybrid.

In order eliminate the need for external image-band filtering, the receiver should acknieve greater than 40dB of image rejection. An important design goal of the LO system is to minimize I-Q phase errors and to provide a high-resolution method of correcting phase error offsets which may exist in the IF<sub>I</sub> and IF<sub>O</sub> paths.

In addition to these specifications, there are many other side goals for the design the LO system. The phase noise of the external LO source to the IC should be the dominant source of noise seen by LO the inputs of the mixers. This will ensure that the implementation chosen does not degrade receiver performance. Furthermore, inductors are avoided in the LO system design to conserve chip area. Finally, a fully-differential signal path is needed to minimize the spurious coupling of unwanted harmonics to the substrate or the supply rails. This helps to maximize the isolation between the LO circuitry and the receiver front-end.

# 2.9 Quadrature Signal Generators

The main function of the LO system is the generation of a pair of quadrature LO signals. Generating a broadband 90° phase shift is relatively easy with passive networks however, keeping the amplitude constant at the same time is quite difficult. Three of the most popular circuit techniques used to generate I and Q signals are: quadrature oscillators[24], RC polyphase filters[25], and frequency divide-by-2 circuits[26].

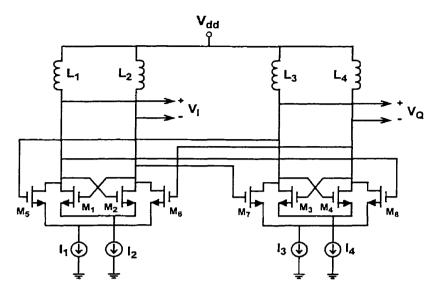

A quadrature LC oscillator, such as the one shown in Figure 2.11, uses a pair of coupled LC oscillators to generate accurate I and Q signals directly. In order to maintain an accurate quadrature output, the oscillator requires the use of closely matched integrated tank resonators which is difficult since mutual couplings between the inductors and surrounding circuitry can limit matching capabilities.

Figure 2.11: Typical CMOS quadrature LC oscillator[27].

Another characteristic of this circuit is that the phase noise of the signals generated are determined by the performance of the oscillator and so if high quality factor inductors are not available in an IC technology, then the phase noise of the LO signals will be degraded. The output frequency of the oscillator also needs to be controlled and thus the use of this circuit demands that supporting circuitry such as a phase locked loop (PLL) be included. In addition to these problems, the quadrature LC oscillator is also susceptible to multi-moding and mode hopping phenomenon.

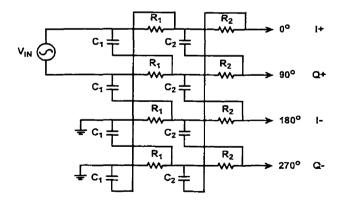

Figure 2.12: Polyphase filter (2-stage).

RC polyphase filters, by contrast, use high-order resistor-capacitor networks to generate quadrature-phased signals from a single phased input[25,28]. Although RC polyphase filters are capable of generating accurate I and Q signals over relatively wide bandwidths, they add attenuation, noise, and typically consume significant chip area[29]. The choice of using either a quadrature oscillator or a single-phased oscillator followed by polyphase filtering to generate quadrature LO signals in a receiver can depend on a number of design constraints such as power dissipation, die area costs, and phase noise requirements[30].

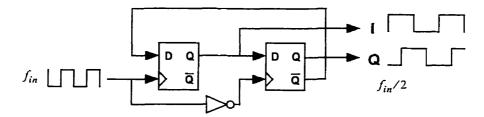

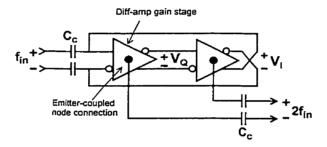

Figure 2.13: Digital divide-by-2, I-Q generator.

Frequency divide-by-2 circuits also generate accurate quadrature LO signals. They typically have a phase error of  $< 1^{\circ}$  over their entire operating range and occupy an area significantly smaller than an equivalently wide-band, RC polyphase filter. Illustrated in Figure 2.13 is a simple digital divide-by-2 formed using a cascade of digital latches. One of the main drawbacks with this technique at high frequencies is that the input frequency  $(f_{in})$  must be twice as high as that of the desired output frequency. Rather than attempt to generate this signal directly, a frequency doubling stage can be used in cascade with the divider to allow the I and Q signals to be effectively generated by an input signal of the same frequency.

In this thesis, frequency doubling followed by frequency division was chosen over the other methods of quadrature generation to allow an externally synthesized, low-phase noise source to be used with the IC, thus removing the need for an integrated quadrature VCO. Doubling techniques explored in later chapters enable frequency division beyond 12GHz, and so the use of an accurate I-Q divider precludes the use of a larger-area polyphase filter.

# 2.10 IC Compatible Methods of Frequency Doubling

Frequency doubling can provide significant system design flexibility in an RFIC. Unfortunately, with the quality factor of integrated inductors typically on the order of 15 or lower, traditional methods of using selective networks to extract a desired harmonic from a non-linear amplifier will, in most cases, have unacceptably poor performance in terms of both area requirements and power efficiency. The art of frequency doubling in microwave systems has almost always involved resonant circuits and so it is not surprising to find that there are very few RFIC-compatible frequency-doubling techniques currently in the literature. Some of the more promising candidates for use in a high-frequency (5-6GHz) application are presented below along with some of their associated drawbacks.

#### 2.10.1 Frequency Multiplier Using Unbalanced Emitter-Coupled Pairs

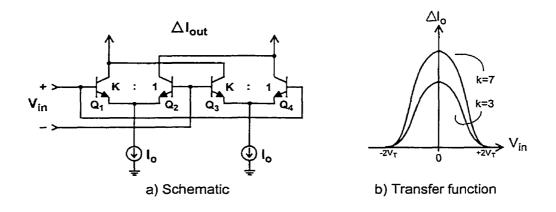

Figure 2.14a shows a frequency-squaring circuit based on a modification of the popular Gilbert-cell mixer topology[31,32].

Figure 2.14: Scaled-emitter Gilbert quad multiplier.

The emitter-coupled transistor pairs of the quad  $(Q_1-Q_2)$  and  $Q_3-Q_4$  have unbalanced emitter areas such that a differential output current  $(\Delta I_{out})$  will exist at the output of the circuit when the voltage across the input terminals  $(V_{in})$  is zero. When the input voltage becomes large (approximately  $> 2V_T$ ) however, the current flow through each half of the circuit becomes balanced and  $\Delta I_{out}$  tends towards zero. In a frequency doubling application, emitter-

scaling factor (K) is chosen to maximize the second-order component of the transfer function illustrated in Figure 2.14b.

It can be shown that the differential output current is,

$$\Delta \text{Iout} = \alpha_F I_o \left\{ \tanh \left( \frac{V_{in} + V_K}{2V_T} \right) - \tanh \left( \frac{V_{in} - V_K}{2V_T} \right) \right\}$$

(2.12)

where  $V_T = kT/q$  is the thermal voltage,  $\alpha_F$  is the dc common-base current gain,  $I_o$  is the bias current,  $V_{in}$  is the input voltage, and  $V_K$  is the offset voltage defined as  $V_K = V_T \ln K$ , where K is the emitter-area scaling parameter [32].

This can then be simplified to,

$$\Delta Iout = \alpha_F I_o \ln K \left\{ 1 - \frac{1}{4V_T^2} V_{in}^2 - \frac{1}{12} (\ln K)^2 \right\} ..., \qquad (2.13)$$

indicating that the differential output current includes a component that is proportional to the square of the differential input voltage. Equation 2.2 also illustrates that the output signal  $(\Delta I_{out})$  has a natural dc offset for a zero volt input. This can be a serious problem in a balanced or fully-differential receiver design since the output current will tend to be slightly biased towards one polarity. Even if capacitive coupling is used to isolate the dc component of this stage from the next, the ac output impedance of the circuit will still be unbalanced due to the different transistor parasitics of the nominal-area devices  $(Q_2 \text{ and } Q_4)$  compared to the scaledarea devices  $(Q_1 \text{ and } Q_3)$ . Such an effect is undesirable since it can degrade the symmetry of the receiver and increase the even-order harmonic distortion of subsequent RF stages.

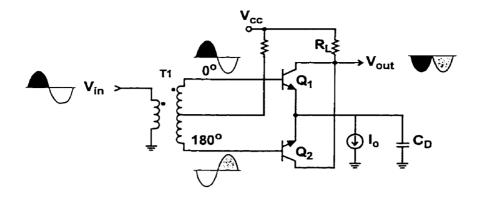

#### 2.10.2 Balun Transformer with Differential-Pair Doubler

Another frequency doubling technique[33] (shown in Figure 2.15) employs an integrated transformer balun to split the input into  $0^{\circ}$  and  $180^{\circ}$  phases and an active rectifying circuit to perform the multiplication. The positive going halves of each phase cause alternating conduction cycles in  $Q_1$  and  $Q_2$  at RF, which generate a rectified output  $(V_{out})$ .

Figure 2.15: Transformer based frequency doubler.

The input signals to  $Q_1$  and  $Q_2$  are intended to be larger than approximately  $2V_T$  to fully switch the transistors on and off, and the decoupling capacitor  $C_D$  (not necessarily an explicit component) prevents current steering from occurring at RF. This effectively causes the transistors to act as individual common-emitter (CE) amplifiers with a common load  $R_L$  such that the input is inverted and rectified to a single-ended output  $(V_{out})$ , resulting in a strong second-order component.

One of the major limitations of this circuit is the single-ended output is ground referred to the supplies and substrate. Employing this type of circuit runs counter to good differential RFIC design, since preventative measures are usually taken throughout the RF signal path to minimize the occurrence of ground loops and the injection of stray currents into the supplies or substrate. It is also difficult to convert a single-ended signal into a fully differential one at RF in an IC, since common-mode rejection of any kind is usually degraded by unwanted parasitic capacitance at key nodes such as the common-emitter node of a differential amplifier. An integrated transformer at the output of  $Q_1$  and  $Q_2$  might be more successful at rejecting common-mode signals, but it too looses its ability to generate a fully-differential output at increased frequencies due to parasitic effects between the input port and the inverting output terminal of the transformer[34].

In addition to the above stated concerns, the area penalty of implementing the integrated transformer  $(T_l)$  on an IC, for the purpose of realizing a frequency doubling circuit is difficult to justify in a low-cost, highly integrated receiver application.

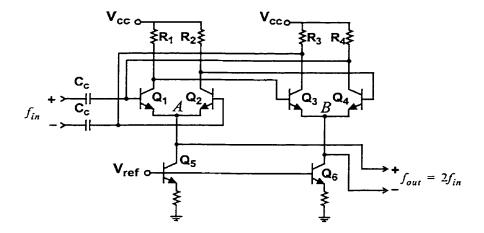

## 2.10.3 An Emitter-Coupled Transistor Pair Frequency Doubler

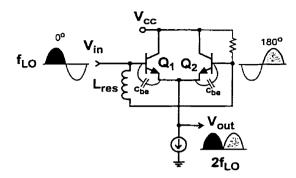

Figure 2.16: Resonator based frequency multiplier.

Figure 2.16 shows a circuit very similar to that of Figure 2.15 except the function of the transformer balun has been replaced with a simple LC-tank resonator (formed by  $L_{res}$  and  $C_{be}/2$ )[35]. With the input signal intended to be larger than approximately  $2V_T$ ,  $Q_I$  and  $Q_2$  are alternately switched into conduction for each positive half-cycle of input as illustrated in the diagram. The transistor which is conducting will act as an emitter follower while the other transistor remains inactive (or reverse biased) thus generating a rectified signal at the emitter-coupled output node.

The fundamental harmonic (or input signal frequency) is typically undesired at the output of a doubler, and in this circuit it is suppressed by the 0° and 180° differential symmetry of the input voltage realized by the tuned LC tank.

One very desirable quality of this topology is that by having an emitter-coupled node as an output, this circuit has the same wideband properties as the emitter follower and can operate successfully to frequencies beyond  $f_T/2$ . In addition, third-order harmonics are suppressed by the differential symmetry of the circuit and thus with the added transistor parasitics at frequencies in excess of approximately  $f_T/10$ , the doubled frequency output is predominantly sinusoidal. Further filtering is typically not required and multiple stages can be easily cascaded.

Unfortunately, this technique also has a single-ended output and requires excessive area for an integrated inductor. Even if chip area is not a concern, the radiating electromagnetic fields and capacitive coupling of the input to the substrate by the inductor can cause undesirable interference with other sensitive circuit blocks in a receiver such as the LNA or its bondwire matching network.

#### 2.11 Summary of IC Frequency Doublers

A few of the more appropriate methods for frequency doubling in an RFIC have been presented along with some of their respective pros and cons. However, none of these techniques are suitable for generating a 10-12GHz differential signal on-chip using a 25 GHz  $f_T$  IC technology. As will be seen in later chapters, a frequency doubler with a fully-differential output is essential in order to obtain an accurate pair of quadrature signals from a frequency divider. To this end, a new regenerative method of frequency doubling, which is compatible with monolithic integration and which has a fully-differential output, is presented in subsequent chapters. The fundamental operation of this new doubler is based on the concept of an injection locked ring oscillator, which the topic of the next chapter.

## **Injection Locked Ring**

### **Oscillators**

There is a renewed interest in some reviving RF techniques and topologies of the past, such as: direct conversion, polyphase filtering, first order frequency synthesis and injection locking to increase the level of functional integration on an RFIC.

In this chapter, a resistively-loaded injection-locked ring oscillator (ILRO) is examined. A Simulink model of the system is also developed and validated through comparisons with HSPICE simulations. This model is then used to provide insight into the fundamental characteristics of the ILRO. Finally, some current and historical uses for simple injection locked oscillators are also briefly mentioned. In later chapters, ILRO based circuits and their characteristics are exploited to perform very useful LO signal processing functions.

#### 3.1 Injection Locking of Oscillators

Injection locking is the process by which a free-running oscillator is synchronized in frequency and phase to an external source. This effect has been observed in many oscillating systems and was first noticed by Huygens in the synchronization of mechanical pendulums[36]. One useful property of an injection locked oscillator is that the phase noise properties of the injecting source are preserved by the locked oscillator because it is locked in phase to the external signal. Thus, if an oscillator with poor free-running phase noise characteristics is locked to a high quality (low-phase noise) source, the phase noise of the locked oscillator is also low.

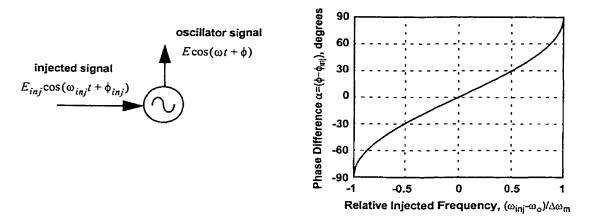

Figure 3.1: Phase of an injection locked oscillator versus the relative injected frequency[37].

For a single tuned oscillator model, it can be shown that the phase of an injection locked oscillator is described by Adler's equation,

$$\frac{d\alpha}{dt} = \omega_o - \omega_{inj} - \underbrace{\frac{E_{inj}\omega_o}{E} \sin(\alpha)}_{\Delta\omega_m} , \qquad (3.1)$$

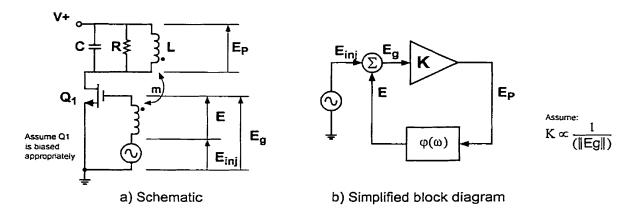

where  $\omega_{inj}$  is the injected signal frequency,  $\omega_0$  is the free-running frequency of the "undisturbed" oscillator, Q is the quality factor of the oscillator's resonator, and  $E_{inj}/E$  is the ratio of the injected signal amplitude to the oscillator's amplitude[38]. The remaining variables are defined in Figure 3.1, where  $\omega$  is the instantaneous frequency of the oscillator and  $\alpha$  is the phase relation between the oscillator and the injected signal (i.e.,  $\alpha = \phi_{inj} - \phi$ ). For a more complete explanation and a full derivation of Adler's equation, see Appendix A.

Using Adler's equation, an oscillator is said to be locked or synchronized to the injected signal if a steady-state solution can be found for the phase such that  $d\alpha/dt = 0$ . Solving (3.1) for steady-state phase gives,

$$\alpha = \sin^{-1} \left( \frac{\omega_{inj} - \omega_o}{\Delta \omega_{ni}} \right) . \tag{3.2}$$

Thus, a solution exists when the injected signal frequency lies within the range,

$$\omega_{ini} = \omega_o \pm \Delta \omega_m \,. \tag{3.3}$$

$\Delta\omega_m$  is often referred to as the "locking range" of the oscillator (even though it only physically represents half the lock range), and although there are always two solutions for  $\alpha$  in equation 3.2, a stability analysis can be used determine which of the solutions is physically realizable. Since only one unique solution to equation 3.2 exists, it can be shown (section II of [38]) that the phase difference between the oscillator and the injected source ( $\alpha$ ) is restricted to,

$$-\frac{\pi}{2} \le \alpha \le \frac{\pi}{2}$$

, for  $\alpha$  in radians. (3.4)

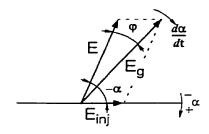

This phase difference as a function of the relative injected signal frequency (i.e., equation 3.2), is plotted in Figure 3.1. Two key observations from this plot are: firstly, that if the oscillator is locked at its free-running frequency, there is no phase shift between the injected signal and the locked oscillator, and secondly that as the locked oscillator's frequency approaches the edge of it's locking range, the phase shift between the injected signal and the oscillator approaches  $\pm 90^{\circ}$ . This is the angle at which the oscillator can no longer be injection locked, and beyond which the oscillator runs freely.

The upper and lower ends of the locking range are referred to as the "locking boundary" frequencies, and are defined as the frequencies beyond which the oscillator cannot remain synchronized to the injected source over an indefinite period of time. The symptoms of an unlocked oscillator near the boundary frequency are easily identified in the lab or in transient simulation. Typically, at the threshold frequency where the oscillator cannot maintain lock, the output is severely amplitude modulated by a low beating frequency and can be observed to slip in and out of lock periodically. The oscillator's output frequency in this condition appears to chirp between the injected signal's frequency and somewhere near it's free-running frequency during each beat cycle. An interesting mechanical model to help visualize the cause of this phenomenon is described in[38].

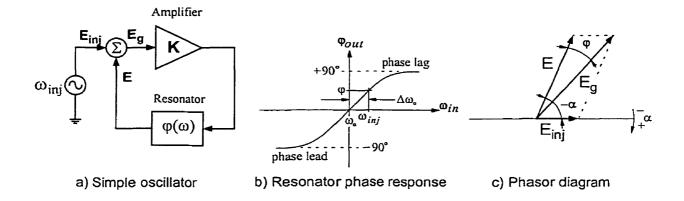

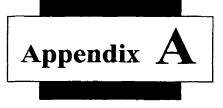

Due to the unique mechanism of oscillator synchronization, most injection-locked oscillators (ILOs) share a number of characteristics. Shown in Figure 3.2a, is a simple block diagram of an ILO (taken from Appendix A).

Figure 3.2: Injection locked oscillator model.

The necessary condition required to injection-lock the oscillator can be derived from equation 3.1 by setting

$$\frac{d\alpha}{dt} = 0, (3.5)$$

and noting that,

$$-1 < \sin(\alpha) < 1. \tag{3.6}$$

This gives

$$\frac{E_{inj}}{E} > 2Q \left| \frac{\Delta \omega_o}{\omega_o} \right|, \tag{3.7}$$

where  $\Delta\omega_0$  is the difference between the frequency of the injected signal ( $\omega_{inj}$ ) and the free-running frequency ( $\omega_0$ ). Figure 3.2b illustrates the phase to frequency response of the single LC section resonator.

From equation 3.7, for a given level of injected signal drive  $E_{inj}$ , we see that an ILO will have a finite band of frequencies ( $\Delta\omega_0$ ) centered around the free-running frequency  $\omega_0$ , over which it is able to become locked. The ratio of  $\frac{\Delta\omega_0}{\omega_0}$  is defined as the relative locking bandwidth of the oscillator and is typically expressed as a percentage. The relative locking bandwidth is directly proportional to the ratio  $\frac{E_{inj}}{E}$ , and inversely proportional to the Q of the

oscillator. This implies that an infinitesimally small level of injected signal is required to lock the oscillator at it's free-running frequency ( $\omega_{inj}=\omega_{o}$ ), and that very high-Q oscillators cannot be locked over a wide frequency range without a large injection amplitude,  $E_{inj}$ .

Figure 3.3: Typical locking range of an ILO.

The typical locking characteristic of an ILO as a function of injected power is plotted in Figure 3.3 for illustration. The steady state phase relationship between the injected signal and the oscillator is depicted in Figure 3.2c and is expressed as,

$$\sin\alpha = 2Q \frac{E}{E_1} \left( \frac{\Delta \omega_o}{\omega_o} \right), \tag{3.8}$$

from equation 3.1 with  $d\alpha/dt = 0$ .

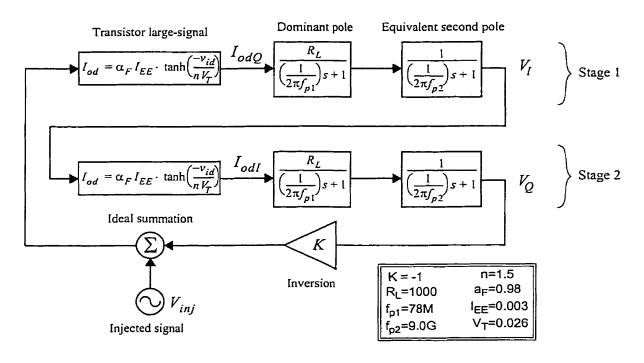

#### 3.2 Simulink Modeling

Some of the injection-locked oscillators employed in this thesis operate at beyond 5GHz and hand calculations quickly become inaccurate and far too tedious to achieve an exact solution as a result of the complicated parasitics,. Transient simulations of a simple differential-pair amplifier operating at 5.5GHz (or  $\sim f_T/5$ ), confirm that the higher-order (small-signal) poles of the amplifier shift with quiescent point, device geometry, signal amplitude, input frequency, and harmonic levels of the input signal. To simplify the analysis, a low-frequency ( $\sim 1$  GHz) version of the oscillators that are employed in this thesis are modeled in this chapter, and serve as a tool to provide insight into the characteristics and the general behaviour of a resistively-loaded, injection-locked ring oscillator running at 5-6GHz.

Understanding the underlying mechanics of the simplified ILRO allow the simulated behaviour of more complicated (and higher frequency) ILROs to be understood, designed and optimized directly using HSPICE computer simulations without the need to calculate or model the poles and zeros of the circuit explicitly by hand.

#### 3.3 Injection-Locked Ring Oscillators

In this section, fundamental mode injection-locking of a quadrature (2-stage) ring oscillator with resistive loads is studied, and an appropriate (simulink) model explaining its operation and characteristics is compared with simulated (HSPICE) results.

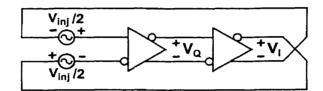

a) Block diagram showing ideal injected signal summation

b) Differential amplifier realization

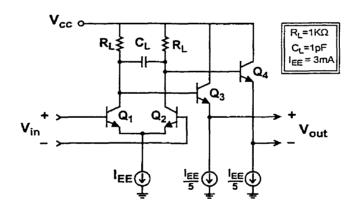

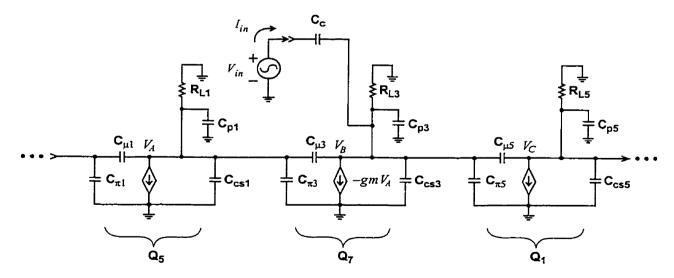

Figure 3.4: Injection locked ring oscillator topology.

Figure 3.4a illustrates a block diagram of a 2-stage differential ring oscillator with a differential injection source placed in series with the feedback path, where the differential amplifiers in the oscillator are shown schematically in Figure 3.4b. In order to simplify the analysis, the  $R_L$ - $C_L$  load of  $Q_I$  and  $Q_2$  is selected to dominate the collector node parasitics and

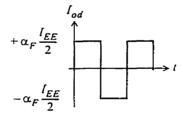

emitter followers  $Q_3$  and  $Q_4$  are employed to reduce the effect of loading from the next stage. The differential output current for the emitter-coupled transistor pair  $Q_1$  and  $Q_2$  of Figure 3.4b can be expressed as [22],

$$I_{od} = \alpha_F \frac{I_{EE}}{2} \cdot \tanh\left(\frac{-\nu_{id}}{nV_T}\right),$$

(3.9)

where  $\alpha_F$  is the dc common-base current gain,  $v_{id} = v_{inj}$  of Figure 3.4b,  $I_{od}$  is the differential output current across the collectors, n is an ideality factor (which depends on process parameters), and  $V_T = kT/q$  is the thermal voltage of the transistors.

The large signal characteristic of a differential-pair of 0.5 x  $10\mu\text{m}^2$  emitter-area devices simulated in HSPICE (at  $I_{EE} = 3\text{mA}$ ) matches equation 3.9 for n = 1.51, and  $\alpha = 0.98$ .  $R_L$  and  $C_L$  for this model are selected to set the free-running frequency of the oscillator to approximately 1GHz (i.e. to  $f_T/25$ ) so that the transistor gain is high and parasitic effects of the transistors can, for the most part, be neglected. Using the component parameters listed in the figure, the dominant pole of the amplifying stage is approximately,

$$f_{p1} = \frac{1}{2\pi \cdot 2k\Omega \cdot 1pF} = 79.6MHz. \tag{3.10}$$

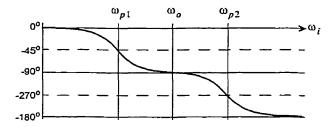

The Barkhausen criteria for oscillation requires that the two amplifying stages in the oscillator contribute a total of 180° of phase shift at the oscillation frequency[39]; another 180° is provided by the cross-coupled feedback connection of the ring. This means that each amplifying stage will provide 90° of phase shift at the free-running frequency.

A simple first-order (low-pass) approximation of each stage is insufficient to determine the free-running frequency of the oscillator ( $\omega_o$ ) since the phase shift of a first order network is given by,

$$\tan^{-1}\left(\frac{\omega}{\omega_{p1}}\right) = \theta_{p1}, \tag{3.11}$$

which can only approach  $90^{\circ}$  for angular frequencies  $\omega \gg \omega_{\rho 1}$  but never reach or surpass it. A two-pole model for each amplifying stage is therefore needed to account for higher-order transistor effects, in which case restating the Barkhausen criteria gives,

$$\theta_{p1} + \theta_{p2} = 90^{\circ} \Big|_{\omega = \omega_{o}}. \tag{3.12}$$

Transient HSPICE simulations of the oscillator in Figure 3.4 dictate the free-running frequency to be 898 MHz at an amplitude of 340 mV-pk. An equivalent second pole can be determined from equations 3.10, 3.11 and 3.12, such that at 898 MHz, a 90° phase shift through the two-pole amplifier realized. For  $f_{pl}$ =79.6MHz, the second equivalent pole frequency is determined to be  $f_{p2}$ =10.13GHz.

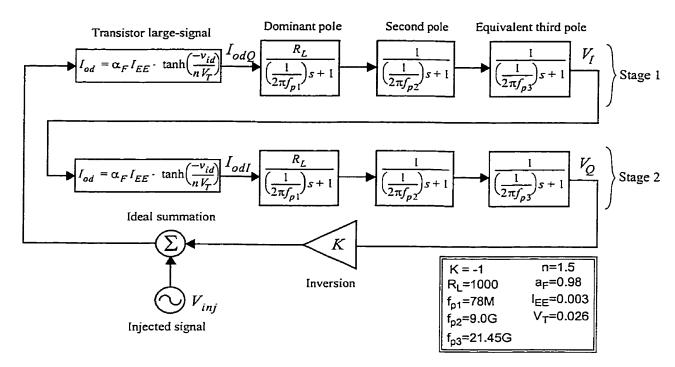

Figure 3.5: Simulink model of the ring oscillator in Figure 3.4.

A Simulink model of the ring oscillator having the topology of Figure 3.4a with the modeled amplifiers of Figure 3.4b is shown in Figure 3.5 along with its associated parameters. In this oscillator model there are two critical variables  $(f_{pl}$  and  $f_{p2})$  available for tweaking. There are also two optimization goals: the oscillator's free-running frequency and output amplitude. HSPICE predicts that the circuit should have a free-running frequency of

$f_{osc}$ =898MHz and an oscillator amplitude of Aosc=340mVp. The original calculations of  $f_{p1}$ =79.6MHz and  $f_{p2}$ =10.13GHz result in  $f_{osc}$ =959MHz and Aosc=295mVp in the Simulink model. This is represents a +3.3% frequency error and -1.2dB amplitude error compared to HSPICE. The amplitude of the oscillator is expected to decrease with increasing frequency, as will be discussed shortly, and so the polarity of the amplitude error is found to be consistent with the frequency error. A possible explanation for this positive frequency shift might be that the higher-order frequency components generated by the tanh function of the transistor large-signal equation, although small, have a non-negligible effect on the zero-crossing of  $v_{id}$ , leading to an unexpected phase shift at the oscillator's fundamental frequency.

Manual optimization of the pole frequencies in the Simulink model to  $f_{pl}$ =78MHz and  $f_{p2}$ =9.0GHz achieves < 0.3% frequency and amplitude error compared to HSPICE simulations of the oscillator in the free-running condition.

#### 3.3.1 Simulink Model versus HSPICE Simulation

Two critical measurements of an injection locked oscillator are the output amplitude as a function of frequency and the locking range as a function of injected signal level. The output amplitude is measured differentially across the quadrature  $(V_Q)$  nodes (as labeled in Figure 3.4a).

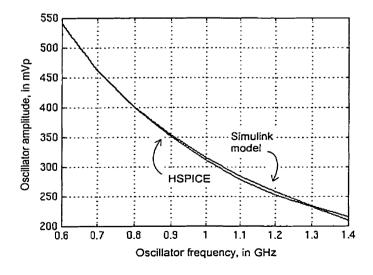

Figure 3.6: Oscillator Amplitude - HSPICE vs. Simulink.

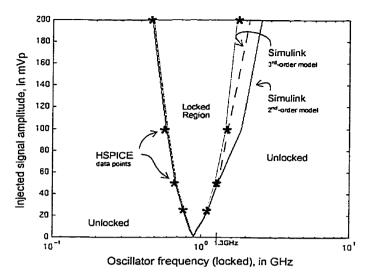

Figure 3.7: Locking range - HSPICE vs. Simulink.

Figures 3.6 and 3.7 show the output amplitude and locking range as a function of frequency for both the HSPICE simulations and the Simulink model. Both are in very close agreement for locking frequencies below 1.3GHz (with a 50mVp injection level). It should be noted that the output amplitude of the simulink model is strongly independent of the injection amplitude.

With the injection level increased to 100mVp, the Simulink model predicts that the upper bound of the locking range is 1.8GHz. HSPICE simulations, however, show an unusual phenomenon above 1.5GHz, whereby the fundamental locking mode of the oscillator is lost and the oscillator begins to act as a frequency halver (or divide-by-2 circuit). In transient simulations, the oscillator's synchronization was observed to slip with respect to the input on every second cycle of the input signal's phase. As a result the oscillator's output frequency was half that of the input signal.

It was hypothesized that this phenomenon might be influenced by the higher-order poles of the active devices in the HSPICE simulation which are not being accounted for in the Simulink two-pole amplifier models. A third pole was introduced into each amplifying half of the oscillator (Figure 3.8) to attempt to validate this hypothesis.

Figure 3.8: An ILRO model using a three-pole amplifier model.

Simulink simulations indeed verified that the frequency halving effect at frequencies above 1.5GHz in HSPICE are captured accurately by introducing a third pole into the model at an empirically determined frequency of  $f_{p3} = 21.45\,GHz$ . Figure 3.7 includes a curve showing the improved correlation between the locking range obtained by the third-order simulink model and the HSPICE simulated results.