# Configurable Computing for Mainstream Software Applications

by

William D. Bishop

A thesis

presented to the University of Waterloo

in fulfilment of the

thesis requirement for the degree of

Doctor of Philosophy

in

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2003

© William D. Bishop 2003

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisisitons et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 0-612-82973-1 Our file Notre référence ISBN: 0-612-82973-1

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou aturement reproduits sans son autorisation.

#### Abstract

A configurable computer is a computing device that may be modified at run-time to provide application-specific computer hardware to support the computation of a task. A coupled configurable computer uses a configurable coprocessor to provide specialized hardware to perform a specific task while the remainder of the computer system works on other tasks. The fact that the hardware functionality of a configurable coprocessor may be specialized at run-time allows this coprocessor to effectively behave like a larger system of coprocessors. Previous research has shown that configurable coprocessors can significantly enhance the performance of an application and/or computer system on niche applications.

This thesis investigates the quantitative and qualitative impacts of configurable coprocessors on the performance of a computer system. A transaction pair model of a configurable coprocessor operation is introduced. This model enables the development of a complete performance model that predicts the behaviour of a coupled configurable computer system. To quantify the parameters used by this model, a series of experiments were conducted. These experiments demonstrate that it is possible to transform an existing computer system into a coupled configurable computer system without the knowledge of the end user. Furthermore, the performance model can be used to predict when it is likely to be advantageous to use a configurable coprocessor to enhance an application and a computer system. The experiments show that the major factors impacting performance of an application are processing time, memory utilization delays, bus utilization delays, and operating system behaviour delays. These findings suggest that a tightly-coupled configurable computer architecture is better suited to mainstream software applications than a loosely-coupled configurable computer architecture.

#### Acknowledgements

I wish to thank my supervisor, Dr. Wayne Loucks, for his patience, his guidance, and his insight. This research would not have been possible without his support and the support of his family. I know Wayne had many sleepless nights throughout the duration of my thesis research. I only hope that I did not contribute significantly to his insomnia.

I wish to thank all of the funding agencies and corporations that supported my research through financial support and gifts-in-kind. In particular, I wish to thank the Natural Sciences and Engineering Research Council (NSERC) of Canada, the Ontario Graduate Scholarship (OGS) Program of the Province of Ontario, and Communications and Information Technology Ontario (CITO), formerly the Information Technology Research Centre (ITRC). I also wish to thank Altera Corporation, Mentor Graphics, Mesquite Software, and Nortel Networks for donating and/or subsidizing hardware and software for the purpose of my research.

Of course, my friends deserve thanks as well. Over the past seven years, I have made many new friendships that will last a lifetime. I particularly wish to thank all of the past and present members of the Parallel and Distributed Systems Research Group at the University of Waterloo.

Most of all, I wish to thank my parents for giving me the support and encouragement that I needed to successfully complete this degree. This thesis would not have been possible without them.

#### **Trademarks**

- [1] SPARCstation is a trademark of SPARC International, Inc. and is licensed exclusively to Sun Microsystems, Inc.. Sun and SunOS are registered trademarks of Sun Microsystems, Inc..

- [2] Altera, MAX, MAX+PLUS, Quartus, FLEX, and SignalTap are registered trademarks of Altera Corporation. AHDL, MAX+PLUS II, Quartus II, FLEX 10K, EPF10K50, APEX, Mercury, Stratix, Cyclone, FastTrack, MegaLAB, Avalon, Nios, RIPP-10, ARC-PCI, and Excalibur are trademarks of Altera Corporation.

- [3] Xilinx, XACT, XC4005, and XC3090 are registered trademarks of Xilinx. XC95108, XC6264, XC6216, XC4025, XC4013, XC4010, XC4003, XC4002, XC3042, XC3030, XC3020, X-BLOX, Configurable Logic Cell, LCA, and Logic Cell are trademarks of Xilinx.

- [4] Synopsys and Synopsys VHDL Compiler are registered trademarks of Synopsys, Inc.. DC Expert, DC Professional, Design Analyzer, Design Compiler, FPGA Compiler, Library Compiler, VHDL Compiler, Synopsys Graphical Environment, VHDL System Simulator, VSS Expert, and VSS Professional are trademarks of Synopsys, Inc..

- [5] Hardware Object Technology, H.O.T., H.O.T. Works, H.O.T. I, H.O.T. II, and H.O.T. III are trademarks of Virtual Computer Corporation.

- [6] Configurable Array Logic, CAL and CAL1024 are trademarks of Algotronix.

- [7] PAL and PALASM are registered trademark of Advance Micro Devices, Inc..

- [8] ABEL is a trademark of Data I/O Corporation.

- [9] Tri-state is a registered trademark of National Semiconductor Corporation.

- [10] Verilog is a registered trademark of Cadence Design Systems, Inc..

- [11] X Windows System is a trademark of the Massachusetts Institute of Technology.

- [12] UNIX is a trademark of AT&T Technologies, Inc...

- [13] IBM and AT are registered trademarks of International Business Machines Corporation and PC/XT and PC/AT are trademarks of International Business Machines Corporation.

- [14] Intel, Pentium, and i486 are registered trademarks of Intel Corporation. VTune is a trademark of Intel Corporation.

- [15] Microsoft, MS, and MS-DOS are registered trademarks of Microsoft Corporation and MS-DOS, MS-Windows, Windows 95, Windows 98, Windows NT, Windows 2000, Windows XP and Win32s are trademarks of Microsoft Corporation.

- [16] HP is a registered trademark of the Hewlett Packard Company.

## Contents

| 1 | Inti | roduction                                                                 | L |

|---|------|---------------------------------------------------------------------------|---|

|   | 1.1  | Motivation                                                                | 1 |

|   | 1.2  | Configurable Computing                                                    | 3 |

|   | 1.3  | Statement of Thesis                                                       | 5 |

|   | 1.4  | Thesis Contributions                                                      | 6 |

|   | 1.5  | Outline of the Thesis                                                     | 7 |

| 2 | Inti | roduction to Configurable Computing                                       | 3 |

|   | 2.1  | Programmable Logic Devices                                                | 8 |

|   |      | 2.1.1 Overview                                                            | 9 |

|   |      | 2.1.2 Programmable Logic Technologies                                     | 9 |

|   |      | 2.1.3 Statically, Dynamically, and Partially Programmable Logic Devices 1 | 1 |

|   |      | 2.1.4 SPLDs (Simple Programmable Logic Devices)                           | 2 |

|   |      | 2.1.5 PIDs (Programmable Interconnect Devices)                            | 5 |

|   |      | 2.1.6 HDPLDs (High-Density Programmable Logic Devices)                    | 6 |

|   |      | 2.1.7 RPUs (Reconfigurable Processing Units)                              | 2 |

|   | 2.2  | Introduction to Modern Computer Architecture                              | 4 |

|   |      | 2.2.1 von Neumann Computer Architecture                                   | 4 |

|   |      | 2.2.2 Personal Computer Architecture                                      | 5 |

|   | 2.3  | Configurable Computer Architectures                                       | 9 |

|   |      | 2.3.1 Types of Configurable Computers                                     | 1 |

|   | 2.4  | Configurable Computing Platforms                                          | 3 |

|   |      | 2.4.1 State-of-the-Art Configurable Computing Machines                    | 3 |

|   | 2.5 | Benefits of Configurable Computing                                            | 35        |

|---|-----|-------------------------------------------------------------------------------|-----------|

|   | 2.6 | Challenges of Configurable Computing                                          | 36        |

| 3 | Mo  | dels of Configurable Computing                                                | 38        |

|   | 3.1 | Introduction to Configurable Computer Models                                  | 38        |

|   | 3.2 | The Transaction Pair Model                                                    | 39        |

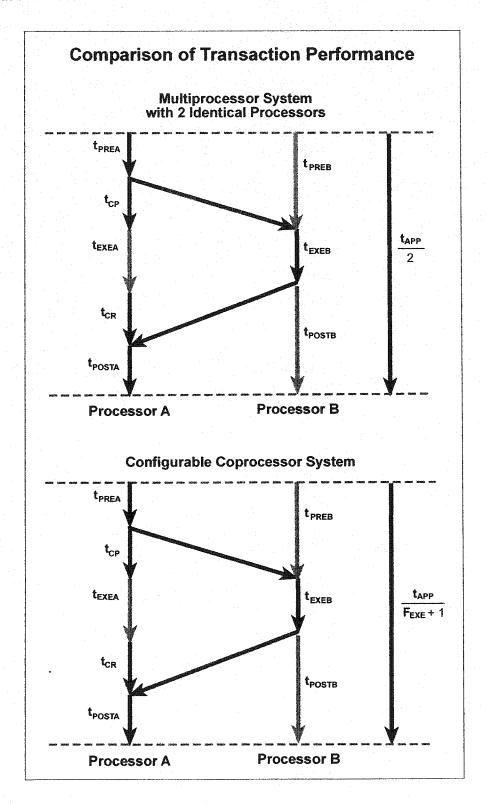

|   |     | 3.2.1 Comparison of Transaction Performance                                   | 43        |

|   |     |                                                                               | 46        |

|   | 3.3 | The Configurable Computer System Performance Model                            | 46        |

|   |     | 3.3.1 Configuration Delays                                                    | 51        |

|   |     | 3.3.2 Memory Utilization Delays                                               | 52        |

|   |     | 3.3.3 Bus Utilization Delays                                                  | 53        |

|   |     | 3.3.4 Operating System Behaviour Delays                                       | 54        |

|   |     | 3.3.5 Processing Times                                                        | 55        |

|   |     | 3.3.6 Evaluating the Net Performance Impact                                   | 56        |

|   | 3.4 | Performance Model Scenarios                                                   | 58        |

|   |     | 3.4.1 General Comments                                                        | 60        |

| 4 | Con | nfigurable Computing Platforms                                                | <b>62</b> |

|   | 4.1 | Platform I: PC + ARC-PCI Board                                                | 62        |

|   |     |                                                                               | 63        |

|   |     | 4.1.2 ARC-PCI Development Kit                                                 | 67        |

|   |     | 그 그 그 그 그 회사 이렇게 하는 그 그 사람들은 하는 것이 되었다. 그 그 그 그 그 그 그 그 그 그 그 그 그 그 그 그 그 그 그 | 69        |

|   |     | 4.1.4 Application Programming Interface                                       | 69        |

|   |     | 4.1.5 Device Driver                                                           | 71        |

|   |     | 4.1.6 Controller Design                                                       | 75        |

|   |     | 4.1.7 User Designs                                                            | 80        |

|   |     | 4.1.8 Comments on PCI Compliance                                              | 84        |

|   |     | 4.1.9 Comments on Performance                                                 | 84        |

|   | 4.2 | Platform II: Nios Embedded Processor Development Board                        | 88        |

|   |     | 4.2.1 The Nios Embedded Processor Development Board                           | 89        |

|   |     | 4.2.2 Nios Embedded Processor Development Kit                                 | 89        |

|   |     | 4.2.3 Configurable Computer Architecture                                      | 92        |

|   |     | 4.2.4 Nios Embedded Processor                       |

|---|-----|-----------------------------------------------------|

|   |     | 4.2.5 User Peripheral Designs                       |

|   |     | 4.2.6 Other Peripherals                             |

|   | 4.3 | Platform III: Sun Workstation                       |

|   | 4.4 | Platform Comparison                                 |

| 5 | Apj | plication 1: CSIM 9                                 |

|   | 5.1 | Introduction to Discrete-Event Simulation           |

|   |     | 5.1.1 Discrete-Event Simulation Terminology         |

|   |     | 5.1.2 Discrete-Event Simulation Tools and Libraries |

|   |     | 5.1.3 Accelerating Discrete-Event Simulation        |

|   | 5.2 | The CSIM Discrete-Event Simulation Library          |

|   |     | 5.2.1 The Choice of CSIM                            |

|   |     | 5.2.2 Modeling Systems with CSIM                    |

|   |     | 5.2.3 Applications of CSIM                          |

|   |     | 5.2.4 Profiling the Performance of CSIM             |

|   | 5.3 | Enhancing CSIM                                      |

|   |     | 5.3.1 Pseudo-Random Number Generation in CSIM       |

|   |     | 5.3.2 Interfacing with Platform I                   |

|   |     | 5.3.3 Performance Optimizations                     |

|   | 5.4 | Experimental Method                                 |

|   | 5.5 | Platform I: Experimental Results                    |

|   |     | 5.5.1 Application Speedup                           |

|   |     | 5.5.2 Evaluation of System Impact                   |

|   | 5.6 | Interesting Observations                            |

|   |     | 5.6.1 Performance                                   |

|   |     | 5.6.2 Impact of Optimizations                       |

|   | •   | 5.6.3 Transparency                                  |

| 6 | App | plication 2: Pseudo-Random Number Generation 11     |

|   | 6.1 | Pseudo-Random Number Generation                     |

|   |     | 6.1.1 Linear Congruential Generators                |

|   |     | 6.1.2 The Choice of Pseudo-Random Number Generation |

|   | 6.2 | Enhar    | ncing Pseudo-Random Number Generation         |

|---|-----|----------|-----------------------------------------------|

|   |     | 6.2.1    | Interfacing with Platform I                   |

|   |     | 6.2.2    | Interfacing with Platform II                  |

|   |     | 6.2.3    | Performance Optimizations                     |

|   |     | 6.2.4    | Platform I Performance Optimizations          |

|   |     | 6.2.5    | Platform II Performance Optimizations         |

|   | 6.3 | Exper    | imental Method                                |

|   | 6.4 | Platfo   | rm I: Experimental Results                    |

|   |     | 6.4.1    | Unbuffered Test Results                       |

|   |     | 6.4.2    | Buffered Test Results                         |

|   |     | 6.4.3    | Unbuffered Test Results on an Uncached System |

|   |     | 6.4.4    | Buffered Test Results on an Uncached System   |

|   |     | 6.4.5    | Measuring the Impact of Caching               |

|   | 6.5 | Platfo   | rm II: Experimental Results                   |

|   | 6.6 | Intere   | sting Observations                            |

|   |     | 6.6.1    | Bus Utilization Delays                        |

|   |     | 6.6.2    | Memory Utilization Delays                     |

|   |     | 6.6.3    | Relative Performance of Processors            |

| 7 | App | olicatio | on 3: Minheap Management 125                  |

|   | 7.1 | Introd   | uction to Minheap Management                  |

|   |     | 7.1.1    | The Choice of Minheap Management              |

|   | 7.2 | Enhar    | ncing Minheap Management                      |

|   |     | 7.2.1    | Interfacing with Platform I                   |

|   |     | 7.2.2    | Interfacing with Platform II                  |

|   |     | 7.2.3    | Hardware Optimizations                        |

|   |     | 7.2.4    | Performance Optimizations                     |

|   | 7.3 | Exper    | imental Method                                |

|   | 7.4 | Platfo   | rm I: Experimental Results                    |

|   |     | 7.4.1    | Unbuffered Test Results                       |

|   |     | 7.4.2    | Buffered Test Results                         |

|   |     | 7.4.3    | Unbuffered Test Results on an Uncached System |

|   |     | 7.4.4   | Buffered Test Results on an Uncached System                 |       |

|---|-----|---------|-------------------------------------------------------------|-------|

|   |     | 7.4.5   | Measuring the Impact of Caching                             |       |

|   | 7.5 | Platfo  | rm II: Experimental Results                                 | . 133 |

|   | 7.6 | Interes | sting Observations                                          |       |

|   |     | 7.6.1   | Algorithm Complexity                                        |       |

|   |     | 7.6.2   | Memory Utilization Delays                                   | . 135 |

|   |     | 7.6.3   | Hardware Optimizations vs. Coprocessor Optimizations        | . 135 |

| 8 | Mod | del Val | lidation                                                    | 137   |

|   | 8.1 | Timin   | g Parameter Estimation                                      |       |

|   |     | 8.1.1   | Assumptions                                                 | . 138 |

|   |     | 8.1.2   | Platform I Configuration Delays                             | . 139 |

|   |     | 8.1.3   | Platform II Configuration Delays                            | . 140 |

|   |     | 8.1.4   | Summary of Configuration Delays                             | . 141 |

|   |     | 8.1.5   | Memory Utilization Observations                             | . 141 |

|   |     | 8.1.6   | Platform I Memory Utilization Delays                        | . 142 |

|   |     | 8.1.7   | Platform II Memory Utilization Delays                       |       |

|   |     | 8.1.8   | Summary of Memory Utilization Delays                        | . 145 |

|   |     | 8.1.9   | Bus Utilization and Operating System Behaviour Observations | . 145 |

|   |     | 8.1.10  | Platform I Lumped Delays                                    | . 146 |

|   |     | 8.1.11  | Platform II Lumped Delays                                   | . 146 |

|   |     | 8.1.12  | Summary of Lumped Delays                                    | . 146 |

|   |     | 8.1.13  | Processing Time Observations                                | . 146 |

|   |     | 8.1.14  | Platform I Processing Times                                 | . 147 |

|   |     | 8.1.15  | Platform II Processing Times                                | . 148 |

|   |     | 8.1.16  | Summary of Processing Times                                 | . 148 |

|   |     |         | Platform Comparison                                         |       |

|   | 8.2 | Compa   | arison of Theoretical Performance with Actual Performance   | . 150 |

|   | 8.3 | Observ  | vations                                                     | . 151 |

|   |     | 8.3.1   | Pre-Processing and Post-Processing                          | . 151 |

|   |     | 8.3.2   | System Profiling                                            | . 151 |

|   |     |         | Dra acceing Times                                           | 150   |

|              |        | 8.3.4   | Application Impact vs. System Impact                      | 152 |

|--------------|--------|---------|-----------------------------------------------------------|-----|

|              |        | 8.3.5   | Performance Model Suitability                             | 152 |

|              | 8.4    | Applic  | ation Implications                                        | 153 |

|              |        | 8.4.1   | Course Computation Granularity                            | 153 |

|              |        | 8.4.2   | Opportunities to Exploit Parallelism                      | 153 |

|              |        | 8.4.3   | Transaction I/O                                           | 154 |

|              | 8.5    | Archite | ectural Implications                                      | 154 |

|              |        | 8.5.1   | Configuration Delays                                      | 154 |

|              |        | 8.5.2   | Memory Utilization Delays                                 | 154 |

|              |        | 8.5.3   | Lumped Delays                                             | 155 |

|              |        | 8.5.4   | Processing Times                                          | 155 |

|              |        | 8.5.5   | Summary of Implications                                   | 156 |

|              |        | clusior |                                                           | 157 |

| 9            |        |         |                                                           | 157 |

|              | 9.1    | 9.1.1   | Contributions                                             |     |

|              |        | 9.1.1   | Challenges of Developing Configurable Coprocessors        |     |

|              |        |         |                                                           |     |

|              |        | 9.1.3   | Mainstream Software Application Speedups                  |     |

|              |        | 9.1.4   | Mainstream Software Application Delays                    |     |

|              |        | 9.1.5   | Desirable Properties of Mainstream Software Applications  |     |

|              |        | 9.1.6   | Desirable Features of Configurable Computer Architectures |     |

|              |        | 9.1.7   | Reference Design for the ARC-PCI Board                    |     |

|              | 0.0    | 9.1.8   | Configuration Delays                                      |     |

|              | 9.2    | 9.2.1   | ial for Future Research                                   |     |

|              |        |         | Profiling of Mainstream Software Applications             |     |

|              |        | 9.2.2   | Analysis of the Impact of System Load                     |     |

|              |        | 9.2.3   | Platform FPGAs and RPUs                                   |     |

|              | 0.2    | 9.2.4   | Translation of Software Algorithms to Hardware Designs    |     |

|              | 9.3    | 1 nesis | Applicability                                             | 104 |

| Bi           | ibliog | graphy  |                                                           | 165 |

| $\mathbf{A}$ | Exp    | erimen  | ntal Results for Transfer Rates                           | 173 |

|              | A.1 Platform I: Windows NT Results                       |       |

|--------------|----------------------------------------------------------|-------|

|              | A.2 Platform I: Linux Results                            | . 174 |

|              |                                                          |       |

| В            | Experimental Results for Pseudo-Random Number Generation | 176   |

|              | B.1 Platform I Results                                   | . 176 |

|              | B.2 Platform II Results                                  |       |

|              | B.3 Platform III Results                                 | . 180 |

|              |                                                          |       |

| $\mathbf{C}$ | Experimental Results for Minheap Management              | 181   |

|              | C.1 Platform I Results                                   | . 181 |

|              | C.2 Platform II Results                                  |       |

|              | C.3 Platform III Results                                 | . 185 |

| D            | CSIM M/M/1 Queue Simulation Model                        | 186   |

## List of Tables

| 2.1  | Comparison of Programmable Logic Technologies           | 10 |

|------|---------------------------------------------------------|----|

| 2.2  | Comparison of Bus Throughput                            | 28 |

| 2.3  | Comparison of Device Throughput                         | 29 |

| 2.4  | Configurable Computer Taxonomy                          | 33 |

| 2.5  | Configurable Computing Systems, Boards, and Devices     | 34 |

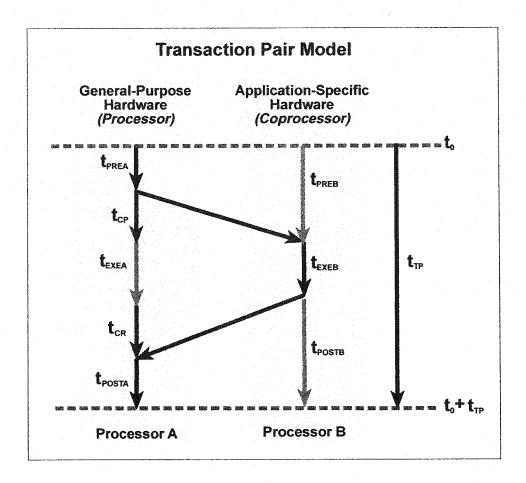

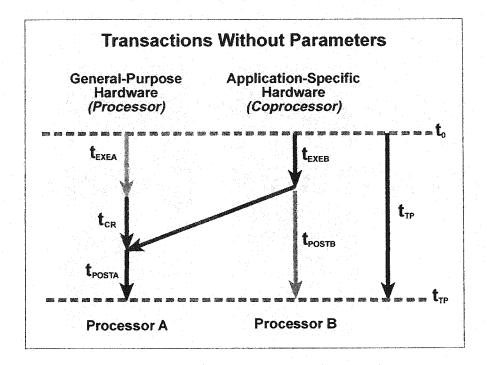

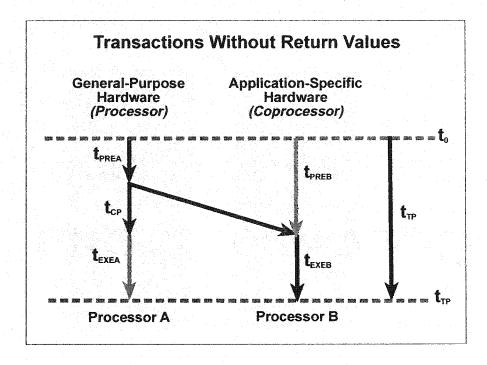

| 3.1  | Transaction Pair Model Timing Parameters                | 41 |

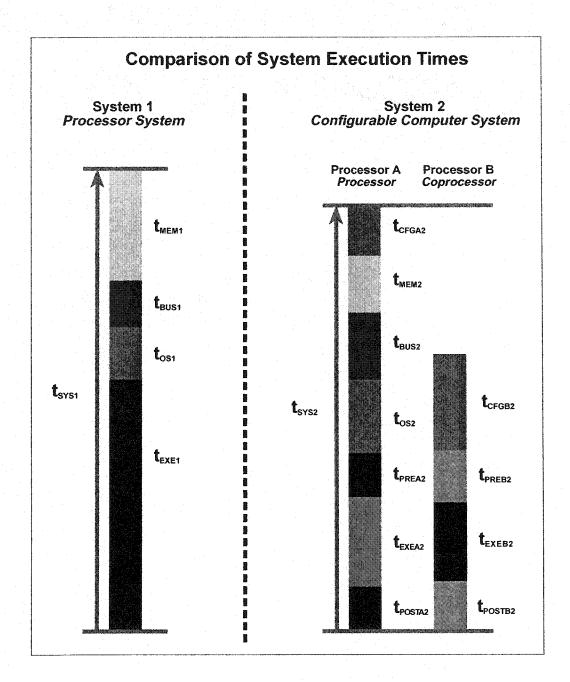

| 3.2  | Performance Model Timing Parameters for System 1        | 48 |

| 3.3  | Performance Model Timing Parameters for System 2        | 49 |

| 3.4  | Timing Parameter Estimates for a Non-Coprocessed System | 58 |

| 3.5  | Timing Parameter Estimates for a Coprocessed System     | 59 |

| 3.6  | Estimated Impact of Timing Parameters                   | 60 |

| 4.1  | Summary of API Functions                                | 71 |

| 4.2  | Summary of Supported Device Driver IOCTLs               | 73 |

| 4.3  | Base Address Regions                                    | 76 |

| 4.4  | Altera FLEX 10K50 Device Configuration Timing           | 79 |

| 4.5  | User Design Handshaking Signals                         | 83 |

| 4.6  | Windows Transfer Comparisons                            | 85 |

| 4.7  | Windows Transfer Times                                  | 87 |

| 4.8  | Linux Transfer Times                                    | 88 |

| 4.9  | Altera APEX 20K200E Device Configuration Timing         | 91 |

| 4.10 | Summary of Computing Platform Processors                | 95 |

| 4.11 | Summary of Computing Platform Coprocessors              | 95 |

| 5.1 | CSIM Object Classes                                                   |

|-----|-----------------------------------------------------------------------|

| 5.2 | CSIM Profiling Results                                                |

| 5.3 | CSIM M/M/1 Performance Results                                        |

| 5.4 | CSIM M/M/1 Speedups                                                   |

| 5.5 | System Profiling Raw Results                                          |

| 5.6 | System Profiling Percentages                                          |

| 6.1 | Unbuffered Test Results                                               |

| 6.2 | Buffered Test Results                                                 |

| 6.3 | Unbuffered Test Results on an Uncached System                         |

| 6.4 | Buffered Test Results on an Uncached System                           |

| 6.5 | Impact of Caching on Performance                                      |

| 6.6 | Platform II Test Results                                              |

| 7.1 | Unbuffered Test Results                                               |

| 7.2 | Buffered Test Results                                                 |

| 7.3 | Unbuffered Test Results on an Uncached System                         |

| 7.4 | Buffered Test Results on an Uncached System                           |

| 7.5 | Impact of Caching on Performance                                      |

| 7.6 | Platform II Blocking Test Results                                     |

| 7.7 | Platform II Non-Blocking Test Results                                 |

| 8.1 | Summary of Configuration Delays                                       |

| 8.2 | Summary of Memory Utilization Delays                                  |

| 8.3 | Summary of Lumped Delays                                              |

| 8.4 | Processing Time Summary                                               |

| 8.5 | Non-Coprocessed Timing Summary                                        |

| 8.6 | Coprocessed Timing Summary                                            |

| 8.7 | Estimated Bounds on System Speedups                                   |

| 8.8 | Actual Application Speedups                                           |

| A.1 | Windows Device Driver Execution Times - Software Timed (WSPEED1A) 173 |

| ۸ ၁ | Windows Davies Driver Execution Times Hardware Timed (WSPEFD1B) 17/   |

| A.3  | Windows Unbuffered Application Execution Times (WSPEED2) |

|------|----------------------------------------------------------|

| A.4  | Windows Buffered Application Execution Times (WSPEED3)   |

| A.5  | Linux Device Driver Execution Times (LSPEED1)            |

| A.6  | Linux Unbuffered Application Execution Times (LSPEED2)   |

| A.7  | Linux Buffered Application Execution Times (LSPEED3)     |

| B.1  | PRAND1                                                   |

|      | PRAND2                                                   |

| B.3  | PRAND3                                                   |

| B.4  | PRAND1NC                                                 |

| B.5  | PRAND2NC                                                 |

| B.6  | PRAND3NC                                                 |

| B.7  | ERAND1                                                   |

| B.8  | ERAND2                                                   |

| B.9  | SRAND1                                                   |

| C.1  | PMIN1                                                    |

| C.2  | PMIN2                                                    |

|      | PMIN3 182                                                |

| C.4  | PMIN1NC                                                  |

| C.5  | PMIN2NC                                                  |

|      | PMIN3NC                                                  |

| C.7  | EMIN1                                                    |

| C.8  |                                                          |

| C.9  | EMIN3                                                    |

| 0.10 | CONTINTAL 105                                            |

# List of Figures

| 1.1  | Classification of Computing Machines                        | 4    |

|------|-------------------------------------------------------------|------|

| 2.1  | Classification of Programmable Logic Devices                | 10   |

| 2.2  | Output Macrocell from a Philips P3Z22V10                    | 13   |

| 2.3  | Architecture of a Philips P3Z22V10                          | 14   |

| 2.4  | A Portion of an Aptix FPIC AX1024R                          | 15   |

| 2.5  | Actel ACT1 Series FPGA Architecture                         | . 18 |

| 2.6  | Actel ACT1 Series FPGA Logic Module                         | 19   |

| 2.7  | Xilinx 4K Series FPGA Architecture                          | 19   |

| 2.8  | Xilinx 4K Series Combinational Logic Block                  | 20   |

| 2.9  | Xilinx 4K Series Input/Output Block                         | 21   |

|      | Altera Flex 10K Series CPLD Architecture                    | 23   |

| 2.11 | von Neumann Computer Architecture                           | 25   |

| 2.12 | Intel 80x86 Processor Family Personal Computer Architecture | 26   |

| 2.13 | Types of Configurable Computer Architectures                | .30  |

| 2.14 | Types of Configuration Modes                                | 31   |

| 2.15 | Types of Configuration Contexts                             | 32   |

| 3.1  | Transaction Pair Model                                      | 40   |

| 3.2  | Transactions Without Parameters                             | 42   |

| 3.3  | Transactions Without Return Values                          | 43   |

| 3.4  | Comparison of Transaction Performance                       | 45   |

| 3.5  | Comparisons of Execution Times                              | 50   |

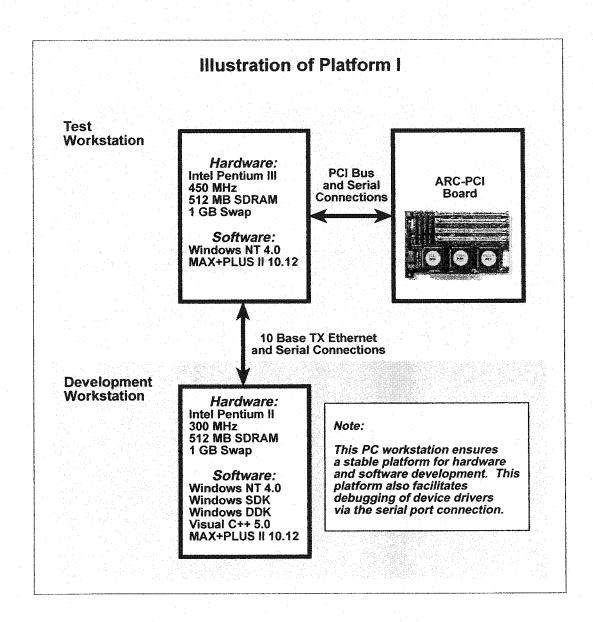

| 4.1  | Illustration of Platform I                                  | 64   |

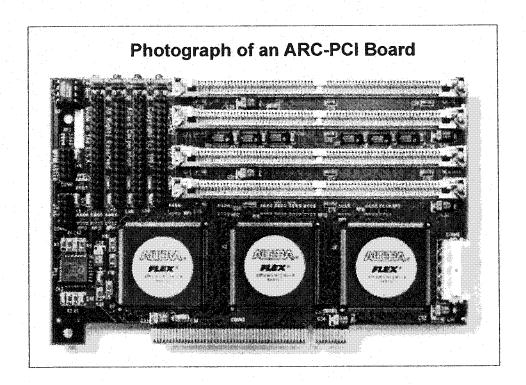

| 4.2  | Photograph of the ARC-PCI Board                         | 65  |

|------|---------------------------------------------------------|-----|

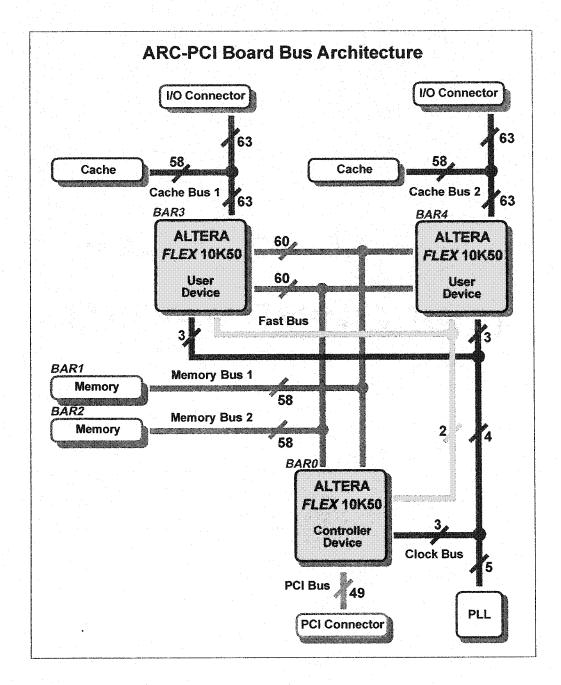

| 4.3  | ARC-PCI Board Bus Architecture                          | 68  |

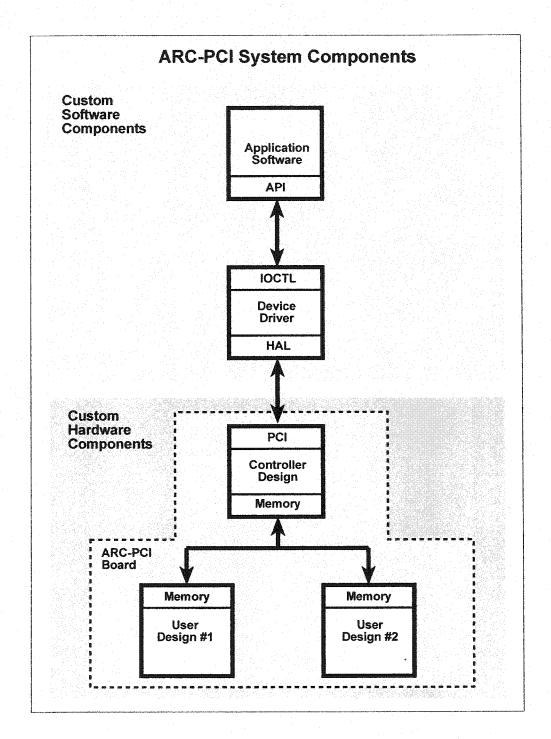

| 4.4  | ARC-PCI System Components                               | 70  |

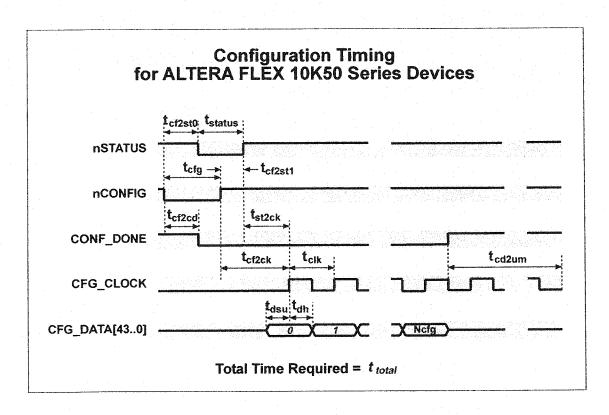

| 4.5  | Configuration Timing for Altera FLEX 10K Series Devices | 78  |

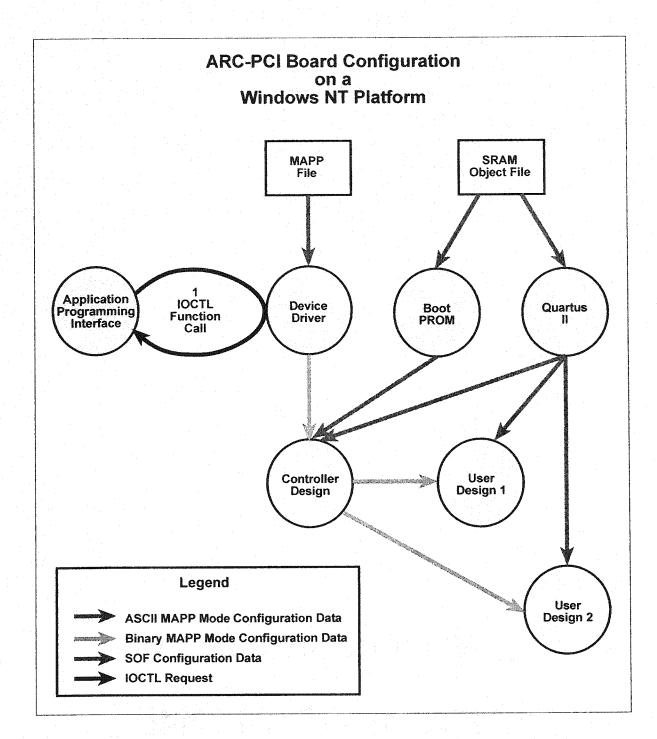

| 4.6  | ARC-PCI Board Configuration on a Windows NT Platform    | 81  |

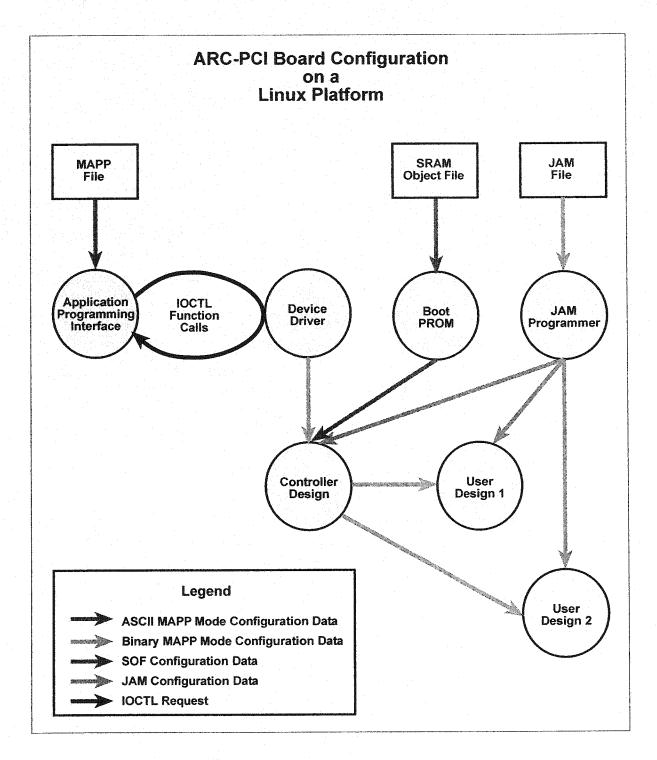

| 4.7  | ARC-PCI Board Configuration on a Linux Platform         |     |

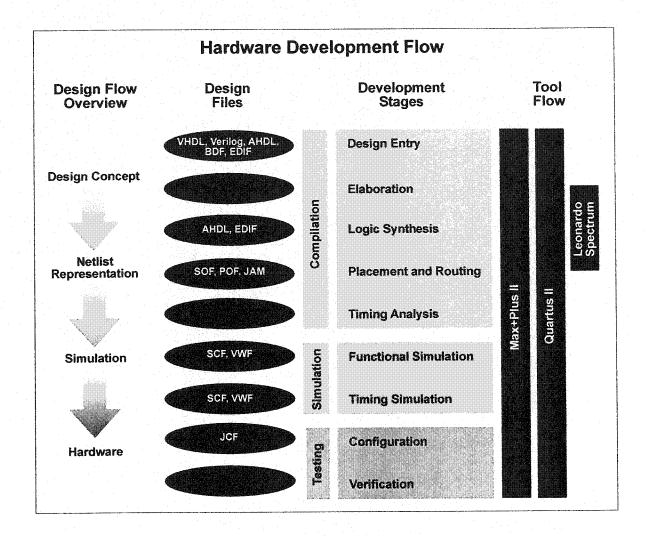

| 4.8  | Hardware Development Flow                               | 83  |

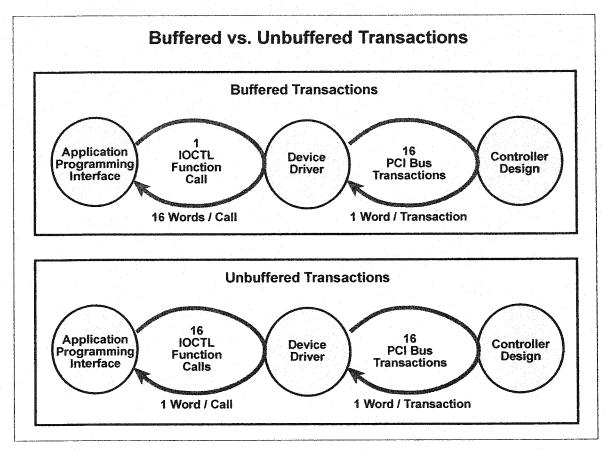

| 4.9  | Buffered vs. Unbuffered Transactions                    | 8€  |

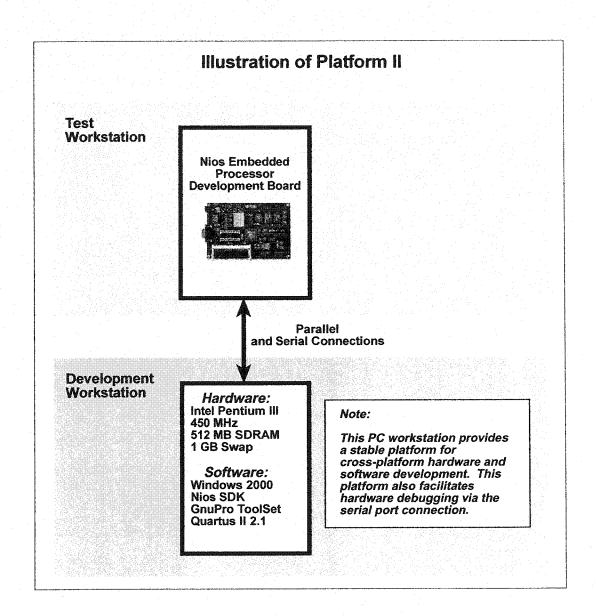

| 4.10 | Illustration of Platform II                             | 90  |

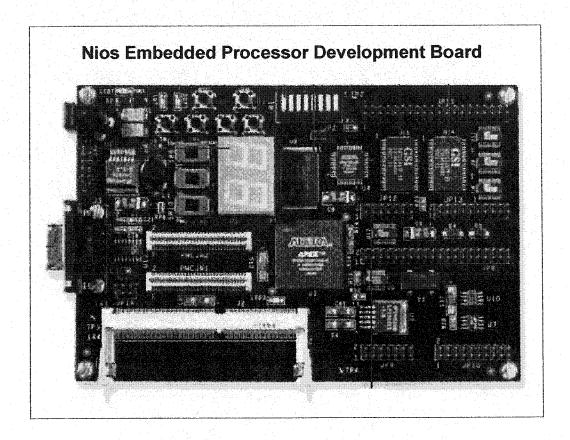

| 4.11 | Nios Embedded Processor Development Board               | 91  |

| 4.12 | Nios Embedded Processor System Components               | 93  |

| 5.1  | Coprocessed CSIM Application                            | 100 |

| 6.1  | Pseudo-Random Number Generator Finite State Machine     | 116 |

| 7.1  | Minheap Interface Finite State Machine                  | 127 |

## Chapter 1

## Introduction

This thesis investigates use of configurable computers for the purpose of enhancing mainstream software applications. Previous research has shown that configurable computers can improve the performance of niche applications. The goal of this research is to quantify, model, and analyze the performance of configurable computers with respect to mainstream software applications. This research explores the feasibility of building a library of configurable hardware components to enhance tasks commonly required by software applications.

#### 1.1 Motivation

Recent advances in the programmable logic device industry have made new approaches to computing feasible. These advances include the following:

Increased Gate Capacity – Modern CPLDs (Complex Programmable Logic Devices) and FP-GAs (Field Programmable Gate Arrays) provide as many as 8,000,000 usable gates using in excess of 100 million transistors. By comparison, the Pentium II processor introduced in May of 1997 consisted of 7.5 million transistors [Int02].

Improved Performance – Devices have been shown to handle clock frequencies in excess of 250 MHz [Von97] and many devices are capable of achieving clock frequencies in excess of

- 66 MHz without the need for floorplanning<sup>1</sup>.

- Reduced Cost In large quantities, programmable logic devices cost about the same as a modern processor. Devices such as the Cyclone [Cor02a] [Cor02b] are significantly less expensive than general-purpose processors.

- **Dynamic Configuration** Dynamic (run-time) configuration has increased the flexibility and usefulness of programmable logic devices.

- Partial Configuration Partial configuration has enabled a portion of a logic device to be configured while the remainder of the device continues normal operation, thus reducing the impact of configuration delays.

- Advanced CAD Tools Innovations in CAD (Computer-Aided Design) tools and the proliferation of HDLs (Hardware Description Languages) have simplified the task of building reusable, custom digital circuits.

In 1997, industry trends indicated that high-speed, partially configurable logic devices with 1,000,000 usable gates would be in production by 2001 [RH97]. This turned out to be a conservative estimate. By the 2nd quarter of 2000, the first commercially available logic device with 1,000,000 usable gates was released. The availability of such devices has spurred interest in the field of configurable computing. The study of configurable computing focuses on the design, implementation, and use of configurable computers. A configurable computer is a computing machine that possesses the ability to adapt its hardware architecture in real-time to the computation at hand. While configurable computers need not utilize programmable logic devices, the existence of such devices has simplified the development of configurable computers.

Configurable computing is based on the principle that a custom computing machine is likely to perform a particular computation more efficiently than a comparable general-purpose machine. A configurable computer's hardware may be customized for a particular computation to exploit parallelism. Traditionally, researchers have focused on the use of configurable computers for bit-serial algorithms exhibiting fine-grained parallelism. Research has shown that programmable logic devices are capable of achieving orders of magnitude of performance improvements compared to

<sup>&</sup>lt;sup>1</sup>Floorplanning is the manual assignment of logic resources and routing resources by a hardware designer. As development tools have improved, the need for this low-level assignment of resources has diminished.

software implementations for certain applications including image processing [AA95], cryptography [VBR<sup>+</sup>96], and hardware emulation [DGJ<sup>+</sup>95]. These niche applications of configurable computing are important to some computer users. However, the majority of computer users rarely have a need for applications such as image processing and hardware emulation.

A few researchers have investigated configurable computing as a means of mainstream computing. The BRASS (Berkeley Reconfigurable Architectures, Systems, and Software) Research Group has investigated the use of programmable logic devices as configurable microprocessors [Deh94]. The goal of the BRASS Research Group was to create one or more microprocessors within a single configurable logic device and then customize the functional units within these microprocessors to the instruction stream. This research has the potential to revolutionize mainstream computing but the complexities of the approach have prevented it from becoming a mainstream computing technique. The most significant problem with this approach is that existing technologies still do not provide sufficient memory bandwidth to support the frequent dynamic configurations required.

Rather than focus on a niche application or struggle with the problems of rapid run-time configuration, this research investigates the development of configurable coprocessors to accelerate common software components. By choosing mainstream software tasks most suitable for acceleration, it is possible to avoid the problem of frequent configuration. The underlying belief is that the achievement of a modest speedup applicable to a broad range of software is more significant to mainstream computing than the achievement of a large speedup applicable only to a single software program. For configurable computing to become a mainstream computing technique, it must be shown that configurable computers are useful for more than just niche applications.

#### 1.2 Configurable Computing

Configurable computing is not a new area of research. The field of configurable computing evolved from research into the reprogrammable and restructurable computers of the 1950's and 1960's. In the early 1960's, Estrin pioneered the development of the first restructurable computer [EBTB63]. His belief was that hardware specialization could enhance the performance of software while simplifying the task of programmers [EBTB63]. Modern configurable computing is based on essentially the same principles although the technology has improved substantially.

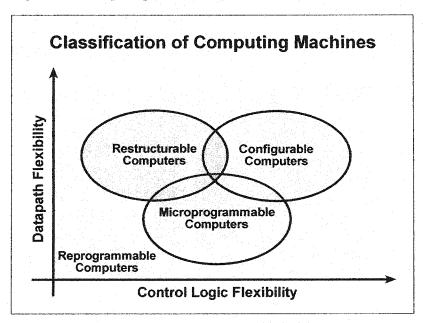

The terms reprogrammable, restructurable, microprogrammable and configurable are not interchangeable. A reprogrammable computer may be programmed to perform different tasks using software. Reprogrammable computers may use a fixed hardware architecture since programmability is provided using software. Virtually all modern computer architectures fall into this class of computers. A restructurable computer uses a network of datapaths to exploit multiple processing units for faster execution of a particular software task. The datapaths of a restructurable computer may be modified at run-time but the control logic elements (i.e., processing units) are fixed. A microprogrammable computer may be programmed at a low-level to emulate a particular instruction set. This provides some control logic flexibility. A configurable computer permits the creation/replacement of one or more processing units as well as modification of the datapaths. This class of computer permits both the configuring of datapaths and control logic at run-time.

Figure 1.1 classifies computing machines into reprogrammable, restructurable, configurable, and microprogrammable machines on the basis of datapath and control logic flexibility. It should be noted that a particular computing machine may fall into two or more classifications.

Figure 1.1: Classification of Computing Machines

The term, configurable computer, is now most often applied to computing machines using dynamically configurable logic. In other words, configurable computers are now synonymous

with a class of computing devices incorporating configurable logic devices that can be configured in-system, often at run-time. This definition is consistent with the use of the term in recent literature.

#### 1.3 Statement of Thesis

It is my thesis that programmable logic devices have the potential to enhance mainstream computing platforms in ways previously unimagined. Programmable logic devices can be integrated into modern personal computers and workstations to provide a means of achieving the benefits of specialized hardware without incurring the costs typically associated with dedicated hardware accelerators. These devices open new possibilities for tasks or algorithms that can benefit from specialized hardware. Even tasks that only marginally benefit from hardware acceleration are potentially suitable for acceleration using a configurable coprocessor.

Tasks commonly implemented in software can be replaced with equivalent configurable hardware components. The tasks to be implemented as configurable hardware components can be determined by profiling target applications. It is likely that tasks such as memory management, queueing, and sorting are good candidates for replacement. Once developed, configurable hardware components, in the form of bitstream files for a particular configurable logic device, may be dynamically loaded into a configurable logic board or configurable logic devices mounted on a customized motherboard. By tightly coupling a configurable coprocessor with the processor of the host computer system, enhanced performance is possible. Software can take advantage of the configurable computing engine by calling specialized functions which communicate with the custom hardware.

In some respects, the approach and its objectives are similar to those of firmware [Opl67]. However, configurable computing is capable of much more than just the resequencing of a set of instructions. Configurable logic permits an entire computer architecture, including the control logic and datapaths, to be configured. Complete hardware specialization is possible. As a result, configurable computing provides flexibility without the degradation of performance sometimes associated with microprogramming-based approaches.

Even a modest improvement in performance may be justifiable for mainstream computing. It

is unreasonable to expect that this approach can achieve orders of magnitudes of performance improvements for mainstream computing applications. Rather than attempt to achieve a huge improvement in a small subset of applications, this research attempts to achieve a modest improvement in a broad range of applications. If configurable logic is ever to enter into mainstream computing, this will be the path required.

#### 1.4 Thesis Contributions

This thesis makes the following contributions to the existing body of literature on configurable computing for mainstream software applications:

- 1. introduces, explains, and validates a novel configurable computing performance model that predicts both application performance and system performance,

- 2. illustrates several of the challenges associated with developing configurable coprocessors,

- provides experimental results demonstrating speedups for two mainstream software applications (pseudo-random number generation and minheap management) executing on a tightlycoupled configurable computer,

- quantifies memory utilization delays, bus utilization delays, and operating system behaviour delays for a mainstream software application (CSIM),

- summarizes several desirable properties of mainstream software applications for configurable coprocessing,

- identifies desirable features of configurable computer architectures to ensure adequate performance,

- 7. describes a reference design for an ARC-PCI Board with hardware support for dynamic configuration and high-speed I/O, and

- shows that configuration delays are not the most significant source of delay for computationallyintensive applications.

#### 1.5 Outline of the Thesis

Chapter 2 introduces the subject of configurable computing by presenting a discussion of the devices, tools, and configurable computing platforms that are commonly used. This chapter also describes some of the challenges of configurable computing. Chapter 3 describes the need for a model of configurable computers. A novel performance model of configurable computing is introduced and described in detail. Chapter 4 describes the test platforms used to obtain the experimental results presented in this thesis. The development process for each configurable computing platform is presented. Chapter 5, Chapter 6, and Chapter 7 describe experiments conducted on mainstream software applications. The first application, CSIM, is a discrete-event simulation library. The second application presented is pseudo-random number generation. The third and final application studied is minheap management, a task not normally implemented in hardware. Chapter 8 validates the performance model using the experimental results. This chapter also notes several interesting observations. Chapter 9 concludes the thesis with a discussion of the thesis contributions and interesting possibilities for future research.

### Chapter 2

# Introduction to Configurable Computing

A configurable computer is a computing device that provides hardware that may be modified at run-time to efficiently compute a set of tasks. Research has indicated price-performance improvements of a factor of 1,000 can be achieved using configurable computing techniques for computation intensive applications [Xil97]. Configurable computing is a relatively new area of research, despite the fact that programmable logic devices have been in existence for several decades. Technological advances now make it possible to exploit the dynamic nature of programmable logic devices. This chapter introduces the technology behind configurable computing and the terminology associated with this new area of research.

#### 2.1 Programmable Logic Devices

The recent interest in configurable computing is largely due to the existence of high-speed, high-density programmable logic devices. The programmable logic device is the basic building block of a modern configurable computer. It provides the ability to modify both the control logic and datapaths of a portion of a computer in real-time. Since modern programmable logic devices evolved from earlier forms of programmable logic devices, no discussion of configurable computing

would be complete without a thorough introduction to programmable logic devices.

#### 2.1.1 Overview

A PLD (Programmable Logic Device) is an integrated circuit that implements a digital circuit designed and programmed by a user. The first programmable logic devices became popular in the 1970's as a replacement for SSI (Small-Scale Integration) and MSI (Medium-Scale Integration) logic [BR96]. These early devices were ideal for implementing interface (also known as "glue") logic and other simple circuits. As programmable logic technology advanced, new forms of PLDs were introduced. The most important of these devices, FPGAs (Field Programmable Gate Arrays) and CPLDs (Complex Programmable Logic Devices), provided the size, performance, and ease of use necessary for experiments in configurable computing.

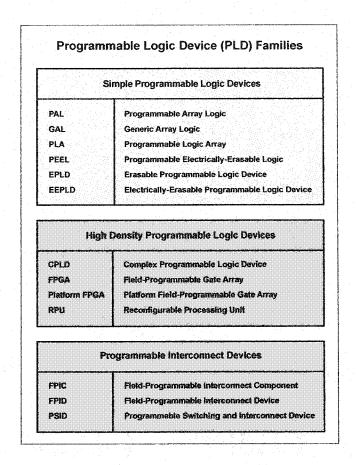

Several classifications of PLDs have been proposed [BR96] [Alt96] [Jen94] [Tri94]. Building upon these classifications, the one shown in Figure 2.1 is proposed. This classification enhances previous ones through the addition of a class for RPUs (Reconfigurable Processing Units). In addition, some new part names recently proposed (Platform FPGAs, and PSIDs) are included in the classification. Each class of PLD is discussed in detail later in this chapter.

#### 2.1.2 Programmable Logic Technologies

Not all programmable logic devices are created equal. The characteristics of a programmable logic device are largely determined by the technology used to construct the programmable logic. Among the technologies used for building a programmable logic device are PROM (Programmable Read-Only Memory), EPROM (Erasable Programmable Read-Only Memory), EEPROM (Electrically Erasable Programmable Read-Only Memory), PLICE (Programmable Low-Impedance Circuit Element) Antifuse, ViaLink Antifuse, Flash SRAM (Static Random Access Memory) and SRAM. These technologies are discussed in detail in the book, "Principles of CMOS VLSI Design: A Systems Perspective" [WE93]. Table 2.1 provides a brief comparison of the features of these technologies.

Of these technologies, only SRAM-based devices with unlimited programming lifetimes are suitable for use in a configurable computing system. All other programmable logic device tech-

Figure 2.1: Classification of Programmable Logic Devices

| Technology       | Volatile | Programming |                    | _        |          |

|------------------|----------|-------------|--------------------|----------|----------|

|                  |          | Method      | Lifetime in Cycles | Density  | Speed    |

| PLICE Antifuse   | No       | External    | 1                  | High     | High     |

| ViaLink Antifuse | No       | External    | 1                  | High     | High     |

| PROM             | No .     | External    | 1                  | High     | High     |

| EPROM            | No       | External    | 10,000 Typical     | High     | High     |

| EEPROM           | No       | External †  | 10,000 Typical     | Moderate | Moderate |

| Flash SRAM       | No       | In-System   | 10,000 Typical     | Moderate | Moderate |

| SRAM             | Yes      | In-System   | Unlimited          | Low      | Moderate |

<sup>&</sup>lt;sup>†</sup> Some EEPROM devices can support in-system reprogramming if the circuit is supplied a programming voltage in addition to the normal supply voltage.

Table 2.1: Comparison of Programmable Logic Technologies

nologies lack the ability to be reprogrammed an unlimited<sup>1</sup> number of times. Any PLD that can be reprogrammed an unlimited number of times is considered to be a *configurable logic device*.

## 2.1.3 Statically, Dynamically, and Partially Programmable Logic Devices

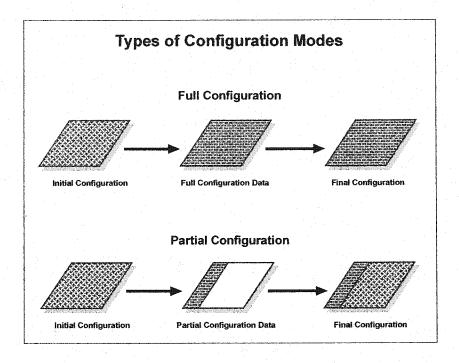

It is sometimes useful to classify PLDs based on the reconfiguration methods the devices support. PLDs are commonly classified into the following three categories: statically-programmable (one-time programmable), dynamically-configurable, and partially-configurable logic devices.

Statically-programmable logic devices may be configured a finite number of times (e.g., 1,000-10,000 times). Although these devices are not suitable for use in a configurable computing system due to their limited lifetime, these devices can be used for computing systems that do not require dynamic (run-time) configuration. Devices based on EEPROM and Flash SRAM technology are examples of statically-programmable logic devices. These devices are suitable for applications such as rapid prototyping and hardware emulation. Although each prototype of the system requires a configuration cycle, it is unlikely that the number of prototypes tested over the usable lifetime of the part will exceed the number of configuration cycles supported by the device. A statically-programmable device is unsuitable for the implementation of a system requiring runtime configuration.

Dynamically-configurable devices may be fully-configured an unlimited number of times. These devices permit the implementation of systems that require configuration at run-time. All dynamically-configurable devices incorporate SRAM technology. A dynamically-configurable device may be used to implement a system that requires frequent configuration.

Partially-configurable devices refer to a subset of dynamically-configurable devices that may be configured one portion at a time. While a subset of the device is configured, the rest of the device continues normal operation. Partially-configurable devices can be used to reduce the amount of time spent waiting for the completion of the configuration of a device at run-time. Partial configuration helps to reduce the delays associated with the configuration of a device.

<sup>&</sup>lt;sup>1</sup>Strictly speaking, the lifetime of a device is limited since all devices eventually fail. A configurable logic device is simply a device whose lifetime is independent of the number of configuration cycles.

This capability is an extremely useful feature for configurable computing.

#### 2.1.4 SPLDs (Simple Programmable Logic Devices)

The term, SPLD, is frequently used to refer to the simplest class of PLDs. The two basic types of SPLDs are PLAs (Programmable Logic Array) and PALs (Programmable Array Logic). The PLA was the first PLD to be manufactured commercially [BR96]. The first PLAs were introduced in the early 1970's but due to high manufacturing costs and poor performance, these devices did not become popular. PLAs are composed of a programmable AND-plane and a programmable OR-plane. These planes provide the equivalent of AND and OR gates using wired logic. Combinations of AND and OR gates may be used to implement any small digital logic circuit within a PLA [Man91].

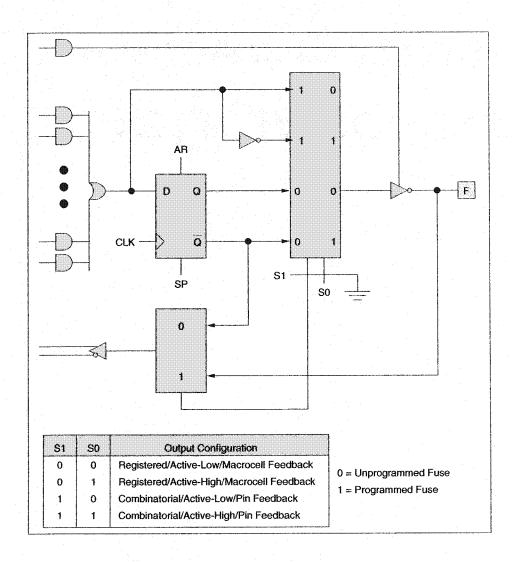

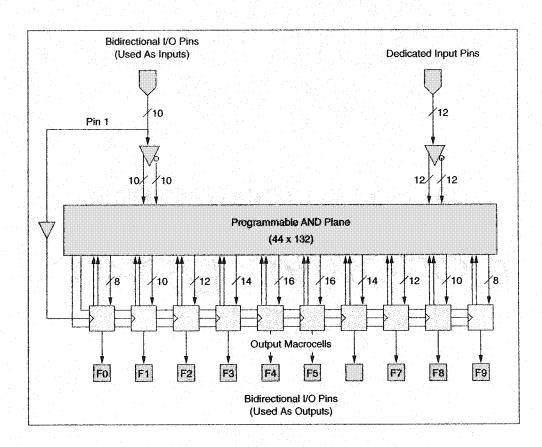

PALs, the second type of SPLD, are also referred to as GALs (Generic Array Logic) or PEELs (Programmable Electrically Erasable Logic), depending upon the manufacturer of the devices. The basic building block of a PAL is called a macrocell. PALs are composed of a set of macrocells connected to an AND-plane. The set of macrocells is sometimes referred to as a fixed OR-plane since each input to a macrocell must pass through an OR gate. PALs are less complex than PLAs yet provide nearly as much flexibility. A PAL may be configured to compute combinatorial and/or registered functions of a small number of inputs. The exact number of inputs varies by part. The number of macrocells in a device often corresponds with the number of outputs leaving the device. An example of an output macrocell from a Philips P3Z22V10 [Phi97] is shown in Figure 2.2.

PALs typically incorporate EPROM or EEPROM technology for performance reasons. EPROM and EEPROM technology are often capable of supporting higher clock frequencies than SRAM technology. A few SPLDs based on SRAM technology exist. A common PAL is the 22V10. This device consists of 10 output macrocells and is therefore capable of generating up to 10 output signals. The architecture of a Philips P3Z22V10 [Phi97], a modern version of an EEPROM-based 22V10, is shown in Figure 2.3.

Due to the use of wide programmable planes (i.e., the AND plane in Figure 2.3), SPLDs are limited in the number of macrocells that can be used effectively. This architecture restricts the size of circuits that can be implemented in a single SPLD. Although SRAM-based SPLDs can

Figure 2.2: Output Macrocell from a Philips P3Z22V10

Figure 2.3: Architecture of a Philips P3Z22V10

be used for small configurable logic designs, they are unsuitable for configurable computing tasks requiring a substantial amount of programmable logic.

#### 2.1.5 PIDs (Programmable Interconnect Devices)

PIDs are a class of PLD specifically designed for switching and routing signals. Although these devices use programmable logic technology, they do not have the capability to compute combinatorial or sequential functions of inputs. Their sole purpose is to route signals from input pins to one or more output pins.

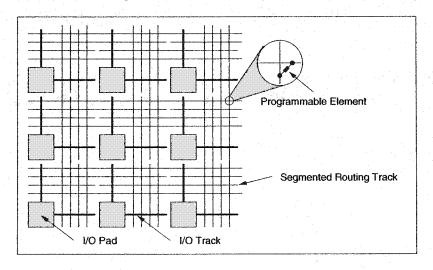

The two best examples of PIDs are FPICs (Field Programmable Interconnect Components) and FPIDs (Field Programmable Interconnect Devices). FPICs are trademarks of Aptix [Apt93] and FPIDs are trademarks of I-Cube [I-C94]. Functionally, FPICs and FPIDs are identical. FPICs and FPIDs use a non-blocking switch matrix based on SRAM technology to route signals from input pins to the appropriate output pins. A portion of an Aptix FPIC architecture is shown in Figure 2.4. These devices use segmented channel routing to connect one or more I/O pads.

Figure 2.4: A Portion of an Aptix FPIC AX1024R

The performance of PIDs has typically been limited to clock frequencies less than 20 MHz [Apt95]. To address this limitation, I-Cube introduced a device known as a PSID (Programmable Switching and Interconnect Device) [I-C97]. PSIDs target applications that require high-speed

switching. PSIDs support frequencies up to 233 MHz [I-C97] through the use of a non-blocking switch matrix and design enhancements that simplify the routing of high-speed busses.

Although PIDs have obvious uses for networking applications, they are also useful for configurable computing. With a PID, it is possible to create a programmable circuit board that allows the routing of signals on the board to be user-defined. Aptix FPCBs (Field Programmable Circuit Boards) [Apt95] are examples of programmable circuit boards. These FPCBs are extremely useful for the rapid prototyping of systems involving multiple PLDs. Since PIDs are based on SRAM technology, the signal routing on the circuit board may be configured as often as required. Given this property, designers of PLD circuits need not fix pin locations for a prototype circuit board early in the design process. This approach simplifies and expedites the prototyping process.

#### 2.1.6 HDPLDs (High-Density Programmable Logic Devices)

As the density of PLD devices increased, new HDPLD (High-Density Programmable Logic Device) architectures were adopted to permit more efficient placement and routing of macrocells. These advanced HDPLD (High-Density Programmable Logic Device) architectures include devices more commonly referred to as FPGAs (Field Programmable Gate Arrays) and CPLDs (Complex Programmable Logic Devices). Although FPGA and CPLD architectures can be quite different, both devices target similar applications (large-scale programmable digital circuits).

Gate arrays and FPGAs (Field Programmable Gate Arrays) are integrated circuits based on the use of a regular array of gates connected by user-defined routing. In the case of an ordinary gate array, the designer is only responsible for creating the masks for the gate array routing (i.e., the metalization layers). This approach reduces the NRE (Non-Recurring Engineering) costs associated with the fabrication of an ASIC device. FPGAs further reduce NRE costs by allowing the designer to route (program) the FPGA after fabrication. FPGAs are generic gate array devices that may be programmed in the field.

FPGAs can be classified by programming technology and by cell topology. The programming technology impacts device density, performance, and reprogrammability. The cell topology impacts device density, performance, and routability. The four FPGA cell topologies are row-oriented, structured array, hierarchical, and sea-of-gate topologies.

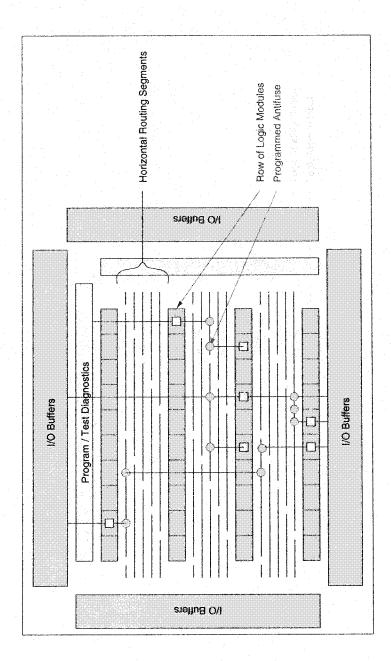

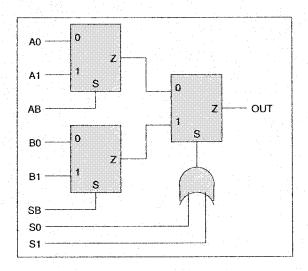

The Actel ACT1 Series FPGA, shown in Figure 2.5, is an example of a row-oriented topology. This device consists of horizontal rows of logic modules. The general-purpose logic module shown in Figure 2.6 may be used to implement simple combinational and sequential logic gates. Between each row, a channel of routing segments is used to route internal signals horizontally. Vertical routing segments (not shown in Figure 2.5 unless used to make a connection) permit the connection of logic modules with horizontal routing segments. The perimeter of a row-oriented device is surrounded by input/output modules connecting internal signals to the I/O pins of the device via buffers.

Row-oriented topologies are often used to implement PLDs based on Antifuse technology. The use of Antifuse technology permits the vertical interconnect to run directly through logic modules. An example of a logic module is shown in Figure 2.6. The ability to run vertical interconnect results in space-efficient, high-performance devices. However, recall that Antifuse technology is not suitable for configurable computing.

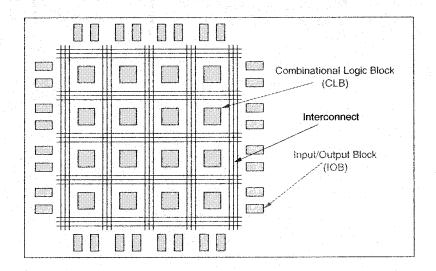

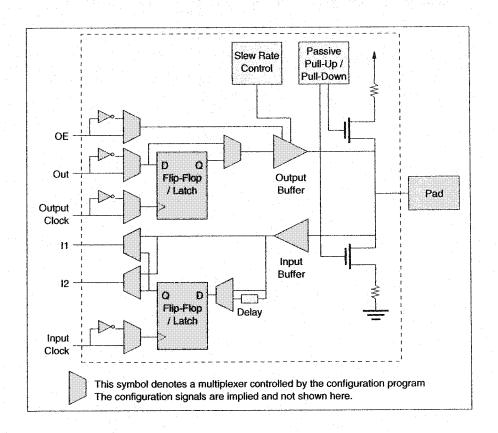

The Xilinx 4K Series FPGA, shown in Figure 2.7, is an example of a structured array topology. The basic building block of this type of array is a CLB (Combinational Logic Block) shown in Figure 2.8. In this architecture, CLBs consisting of LUTs (Look-Up Tables) and flip-flops are arranged in a matrix. This FPGA architecture is sometimes called island-style since each CLB is surrounded by horizontal and vertical routing channels. At the perimeter of the device, IOBs (I/O Blocks) are placed to connect internal signals to the I/O pins. An example of an IOB is shown in Figure 2.9.

Island-style FPGA topologies are common. FPGAs based on structured array topologies are simple to understand and easily expandable. The trade-off between density and routability may be adjusted by simply adding or removing routing segments. Similarly, device size may be increased by simply adding new rows and/or columns of CLBs along with the appropriate routing segments.

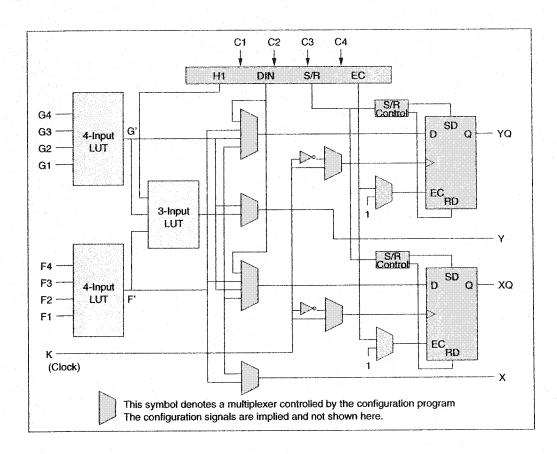

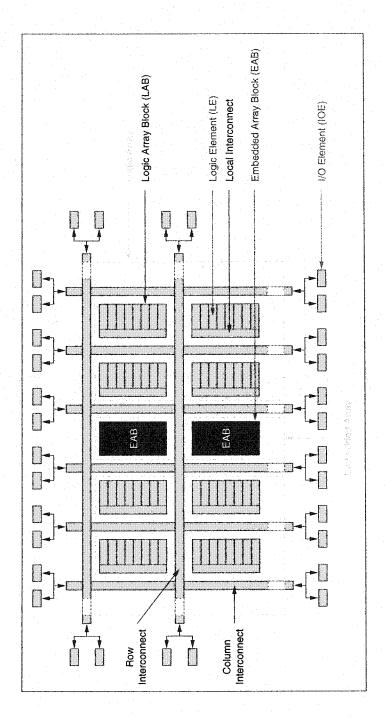

CPLDs (Complex Programmable Logic Devices) are an example of a hierarchical PLD. Most, but not all, CPLDs consist of a hierarchy of smaller PLDs. For example, a hierarchy of 22V10 devices may be connected to form a CPLD. Devices such as the Altera MAX 7000 Series are an example of this type of CPLD. However, CPLDs also include devices that might otherwise be classified as FPGAs. An example of a CPLD architecture is shown in Figure 2.10. The Altera Flex10K architecture resembles that of an island-style FPGA. This device is considered to be a

Figure 2.5: Actel ACT1 Series FPGA Architecture

Figure 2.6: Actel ACT1 Series FPGA Logic Module

Figure 2.7: Xilinx 4K Series FPGA Architecture

Figure 2.8: Xilinx 4K Series Combinational Logic Block

Figure 2.9: Xilinx 4K Series Input/Output Block

### CPLD for the following reasons:

- 1. It consists of a hierarchy of LABs (Logic Array Blocks) that resemble SPLDs.

- 2. The ratio of flip-flops to combinational logic gates is not nearly as high as the ratio found in a typical FPGA.

- 3. It directly supports functions of a large number of inputs.

- 4. The performance of the device is more predictable than the performance of a typical FPGA due to its non-segmented routing.

The sea-of-gates topology was popular in the late 1980's prior to the merger of Algotronix and Xilinx. The Algotronix CAL1024 device is an example of a sea-of-gates device. It is no longer commercially produced. As device densities increased, the sea-of-gates topology was phased out of development. The routing of a sea-of-gates device posed a difficult problem for modern CAD tools due to the amount of flexibility provided by the architecture. More restrictive topologies were found to be much easier to place-and-route.

Regardless of the topology, FPGAs and CPLDs are the highest density PLDs on the market with gate counts approaching 8,000,000 usable gates. Very complex devices incorporating built-in functional units and high-speed serial I/O have been introduced. These technological advances further improve the density and performance of devices. SRAM-based HDPLDs are the building blocks of modern configurable computers.

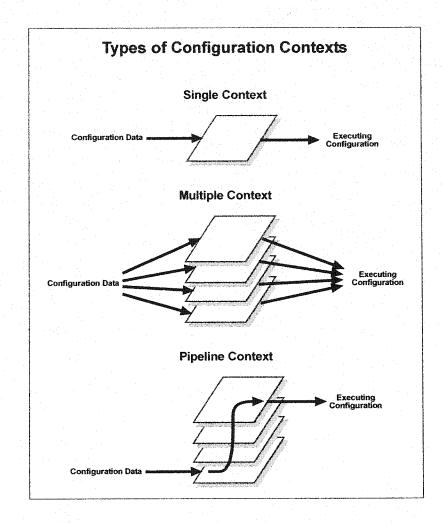

# 2.1.7 RPUs (Reconfigurable Processing Units)

The term RPU was first proposed by Steve Casselman of Virtual Computing Corporation [Cas96]. This class of PLD includes FPGAs and CPLDs with special enhancements to support partially configurable computing. These devices provide mechanisms for high-speed partial configuration. Hardware components may be swapped into and out of a single device in real-time. In addition, these devices provide built-in functional units to improve the performance of common operations such as addition and bit-shifting. Instead of building upon arrays of combinational logic blocks and logic elements, RPUs often build upon arrays of simple processing units. Over 20 different variations of RPUs have been documented [Har01].

Figure 2.10: Altera Flex 10K Series CPLD Architecture

The DPGA (Dynamic Programmable Gate Array) [Deh94] proposed by André Dehon at MIT was one of the first RPU designs. This chip included a small on-chip instruction memory to assist with context-switching. Based on this device, the TSFPGA Time-Switched Field Programmable Gate Array [Deh96] and the MATRIX [MD96] RPUs were developed. The Colt device developed by Peter Athanas is another example of an RPU. It tackles the problem of context-switching using a technique known as Wormhole Run-Time Reconfiguration [BAM96].

The Xilinx XC6200 Series devices are the only commercial devices on the market that may be classified as RPUs. These devices support partial configuration and provide dedicated logic for the implementation of important functions. The Xilinx XC6200 Series devices are also the first commercial devices to have a public-domain bitstream format. All other PLDs use proprietary bitstream formats for device programming. For this reason, these devices have been widely adopted for research into configurable computing. Research conducted by Xilinx in August 1997 indicated that more than 100 research institutions around the world had acquired Xilinx XC6200 Series devices for research [Xil97].

# 2.2 Introduction to Modern Computer Architecture

Modern computer architecture has evolved since the early days of computing. Technological advances have permitted the development of complex computer architectures. However, the fundamentals of computer architecture remain the same. All computers consist of processing units, storage devices, input/output devices, and interconnection structures. The number of processing units and storage devices supported, the types of processing units and storage devices supported, and the interconnections among processing units and storage devices may differ but the building blocks remain the same.

# 2.2.1 von Neumann Computer Architecture

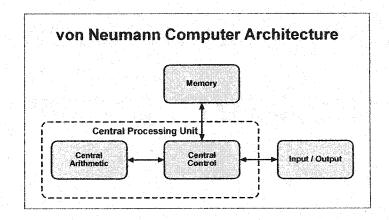

John von Neumann introduced a fundamental model of computation in 1945 when he drafted a report [vN45] on the EDVAC (Electronic Discrete Variable Automatic Computer). The von Neumann Computer Architecture [God93a] has become the foundation of modern computer architecture. The von Neumann Computer Architecture consists of a Central Control [Unit], a Central

Figure 2.11: von Neumann Computer Architecture

Arithmetic [Unit], a Memory, and Input / Output [Devices] as shown in Figure 2.11 [God93b]. The Central Control [Unit] and the Central Arithmetic [Unit] combine to form a CPU (Central Processing Unit). The von Neumann Computer Architecture is based on the stored program concept. A program is a sequence of instructions to be executed. Prior to execution, the Memory is loaded with a program. Upon execution, the Central Control [Unit] reads an instruction in Memory, decodes the instruction, and performs the tasks associated with each instruction. Although simple in concept and design, the von Neumann Computer Architecture provides the flexibility necessary to build a general-purpose computer capable of performing a complex sequence of computations.

### 2.2.2 Personal Computer Architecture

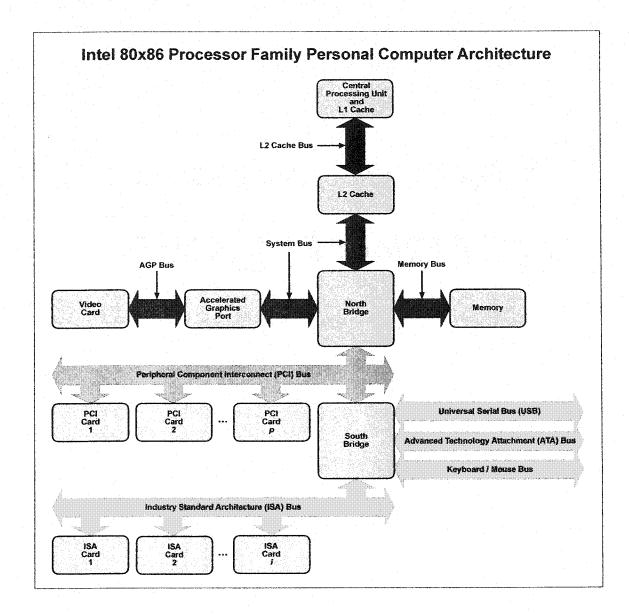

Personal computers based on the Intel 80x86 Processor Family have dominated the computer marketplace for the past two decades. Personal computer architecture has evolved from an architecture quite similar to the von Neumann Computer Architecture into the complex architecture shown in Figure 2.12. Enhancements and technological innovations have been incorporated into the architecture while maintaining backward compatibility with legacy devices.

One key difference between the von Neumann Computer Architecture and the Intel 80x86 Processor Family Personal Computer Architecture is that the CPU does not connect directly with all other functional units and devices. A hierarchy of busses and bridges allow the interconnection

Figure 2.12: Intel 80x86 Processor Family Personal Computer Architecture

of both high-speed devices and legacy devices. This hierarchy provides more opportunities for the CPU to work on one task while devices work independently on other tasks. This architectural feature is an example of low-level parallelism. The CPU operates on a single instruction stream but the completion of an instruction may cause a device to start performing a task while the CPU continues executing its instruction stream.

This noticeable change in computer architecture results from a desire for high system performance while maintaining backwards compatibility with legacy devices. The bus hierarchy allows slower, legacy devices to connect to a high-speed processor without significantly reducing the performance of the CPU on other tasks. The CPU, the busses, and the devices often operate at different clock frequencies. The CPU may eventually be forced to wait for a slow device to complete an operation. However, if the CPU is capable of executing instructions while waiting for a slow device to respond to a request, overall system performance improves.

Clearly, the introduction of independence between functional units and devices within a computer blurs the line between sequential and parallel processing. Personal computers are capable of computing several tasks in parallel. However, this low-level parallelism does not change the sequential nature of the instruction stream. All of the low-level parallelism may be hidden from the end user<sup>2</sup>. For this reason, modern computer architectures are considered to be examples of sequential computers. The term parallel computer is commonly associated with computing machines that expose the existence of two or more processing units.

#### Performance Limitations in Personal Computers

There are limits to the performance benefits that can be achieved by adding more devices and busses to a computer architecture. A bus hierarchy introduces synchronization points. When two busses wish to share information, synchronization between the busses is necessary. Bridges attempt to alleviate synchronization bottlenecks by scheduling bus transactions and buffering responses to reduce the impact of synchronization. Bridges effectively tradeoff bus latency for increased throughput. By using the time spent waiting for a slower bus to respond to a request effectively, it is possible to improve overall system performance.

<sup>&</sup>lt;sup>2</sup>Operating systems often expose some of the parallelism through the use of kernel functions and application libraries to allow programmers to exploit the hardware more aggressively.

| Com | parison | of Bus | Throughput |

|-----|---------|--------|------------|

|     |         |        |            |

| Name         | Maximum<br>Data Width | Peak<br>Frequency | Peak<br>Throughput | Performance<br>Comparison<br>Relative to |  |

|--------------|-----------------------|-------------------|--------------------|------------------------------------------|--|

|              | (bits)                | (MHz)             | (Mbits / s)        | ISA Bus                                  |  |

| System Bus   | 32                    | 533               | 17056              | 107                                      |  |

| AGP Bus (4X) | 128                   | 66                | 8448               | 53                                       |  |

| PCI Bus      | 64                    | 66                | 4224               | 26                                       |  |

| Firewire Bus | 1                     | 3200              | 3200               | 20                                       |  |

| ATA/100 Bus  | 32                    | 25                | 800                | 5                                        |  |

| SCSI-3 Bus   | 16                    | 40                | 640                | 4                                        |  |

| USB 2.0 Bus  | 1                     | 480               | 480                | 3                                        |  |

| ISA Bus      | 16                    | 10                | 160                | 1                                        |  |

Table 2.2: Comparison of Bus Throughput

As devices and busses are added, the control logic increases in complexity. This additional complexity can restrict performance. Personal computer architectures have traditionally sacrificed performance for backwards compatibility and flexibility. For example, support for the 16-bit ISA (Industry Standard Architecture) Bus still exists in many personal computers. The throughput of the ISA Bus is approximately three orders of magnitude less than that of a modern CPU. The issue rate for a CPU can be two 32-bit instructions per clock cycle at a clock rate of 2 GHz. This is effectively a rate of 32-bits per 250 ps. Legacy ISA Cards operate on 16-bit instructions per bus cycle at a bus rate of 8 MHz<sup>3</sup>. This is effectively a rate of 32-bits per 250 ns. Therefore, a modern CPU issues instructions approximately 1000 times faster than the ISA Bus. This throughput difference can result in significant delays when synchronization between two busses occurs. The bridges connecting busses in the bus hierarchy attempt to minimize these delays by buffering and reordering bus transactions. However, these delays can never be eliminated. For example, a PCI bus transaction always impacts the system bus. A comparison of the throughput of busses is provided in Table 2.2 and a comparison of the throughput of devices is provided in Table 2.3.

$<sup>^3</sup>$ Strictly speaking, the clock frequency of an ISA card can range from 6 MHz to 10 MHz, depending upon the CPU clock frequency

| Comparison | of | Device | Thro | ughput |

|------------|----|--------|------|--------|

|            |    |        |      |        |

| Name           | Maximum<br>Data Width<br>(bits) | Peak<br>Frequency<br>(MHz) | Peak<br>Throughput<br>(Mbits / s) | Performance<br>Comparison<br>Relative to<br>CD-ROM |

|----------------|---------------------------------|----------------------------|-----------------------------------|----------------------------------------------------|

| Pentium IV CPU | 64                              | 2600                       | 166400                            | 2667                                               |

| Ethernet       | 1                               | 1000                       | 1000                              | 16                                                 |

| Hard Disk      | 1                               | 352                        | 352                               | 6                                                  |

| CD-ROM (52X)   | 8                               | 8                          | 62                                | 1                                                  |

Table 2.3: Comparison of Device Throughput

# 2.3 Configurable Computer Architectures

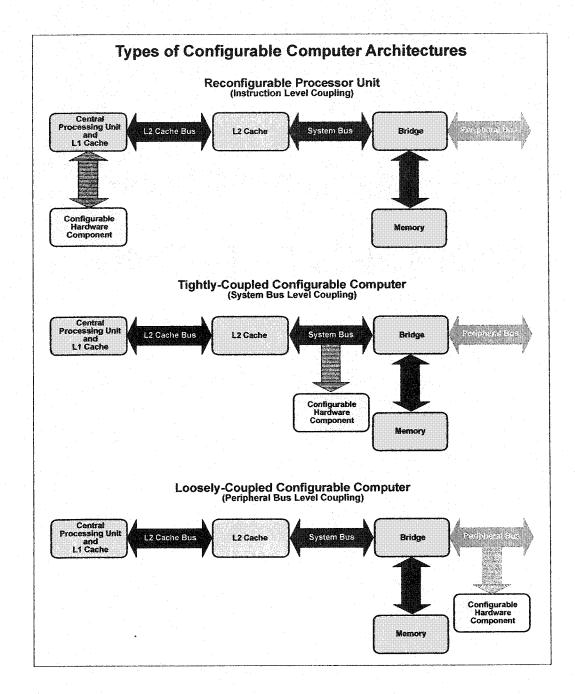

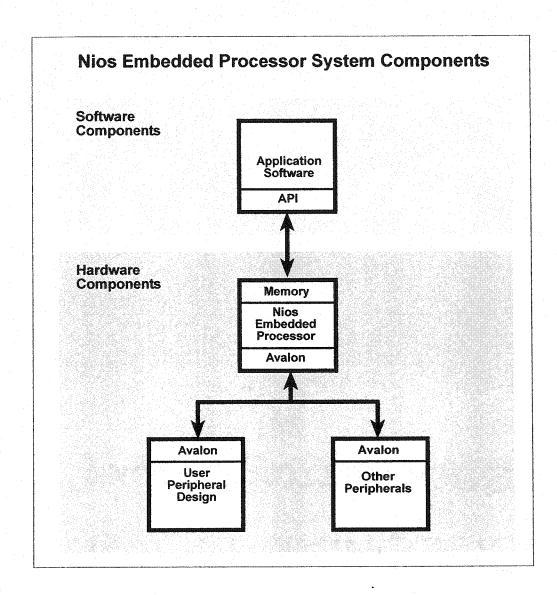

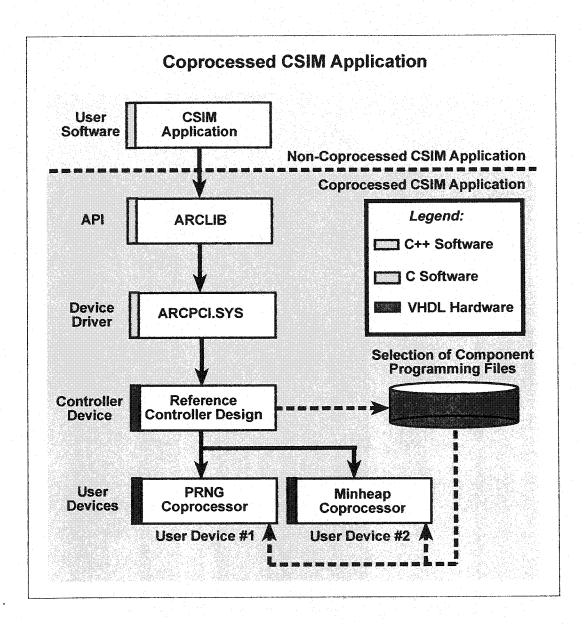

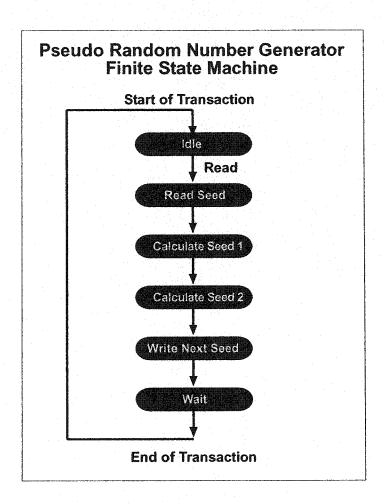

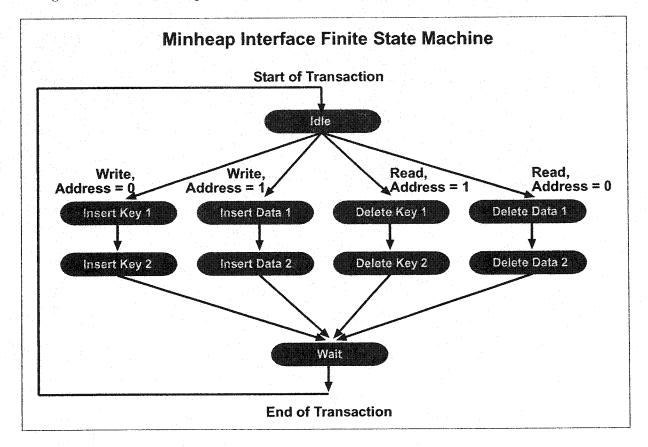

Configurable computers use configurable hardware structures to provide a level of hardware flexibility not found in ordinary computer architectures. Configurable computer architectures typically consist of a fixed, general-purpose hardware component and a configurable, application-specific hardware component. The general-purpose hardware component may be a processor core or a complete general-purpose computer system. The application-specific hardware component is typically one or more HDPLDs configured for a particular task. The two components may be coupled at the instruction level, the system bus level, or the peripheral bus level as shown in Figure 2.13. A computer that uses configurable hardware at the instruction-level is referred to as a reconfigurable processor unit. A computer that couples configurable hardware with a CPU at the system bus level is referred to as a tightly-coupled configurable computer. A computer that couples programmable hardware with a CPU at the peripheral bus level is referred to as a loosely-coupled configurable computer.